参数资料

| 型号: | HW-XGI-VIDEO-US |

| 厂商: | Xilinx Inc |

| 文件页数: | 48/68页 |

| 文件大小: | 0K |

| 描述: | DAUGHTER CARD VIDEO I/O VIODC |

| 标准包装: | 1 |

| 其它名称: | 122-1506 HW-XGI-VIDEO-US-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

�� �

�

�

�Chapter� 6:� SDI� Interface�

�Table� 6-5:�

�ADV7321B� Register� Settings� for� PAL� (Continued)�

�R�

�Register�

�Name�

�SD� Fsc� 2�

�SD� Fsc� 3�

�Address�

�0x4E�

�0x4F�

�Value�

�0x09�

�0x2A�

�Description�

�SDI� Transmitter�

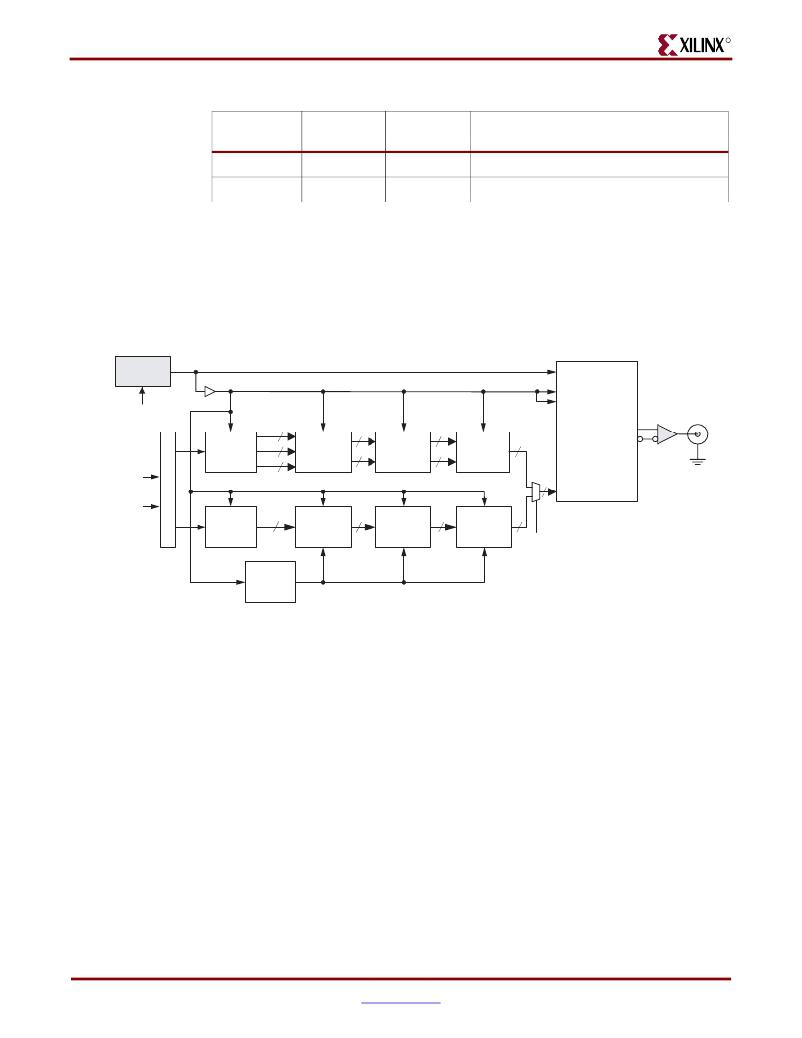

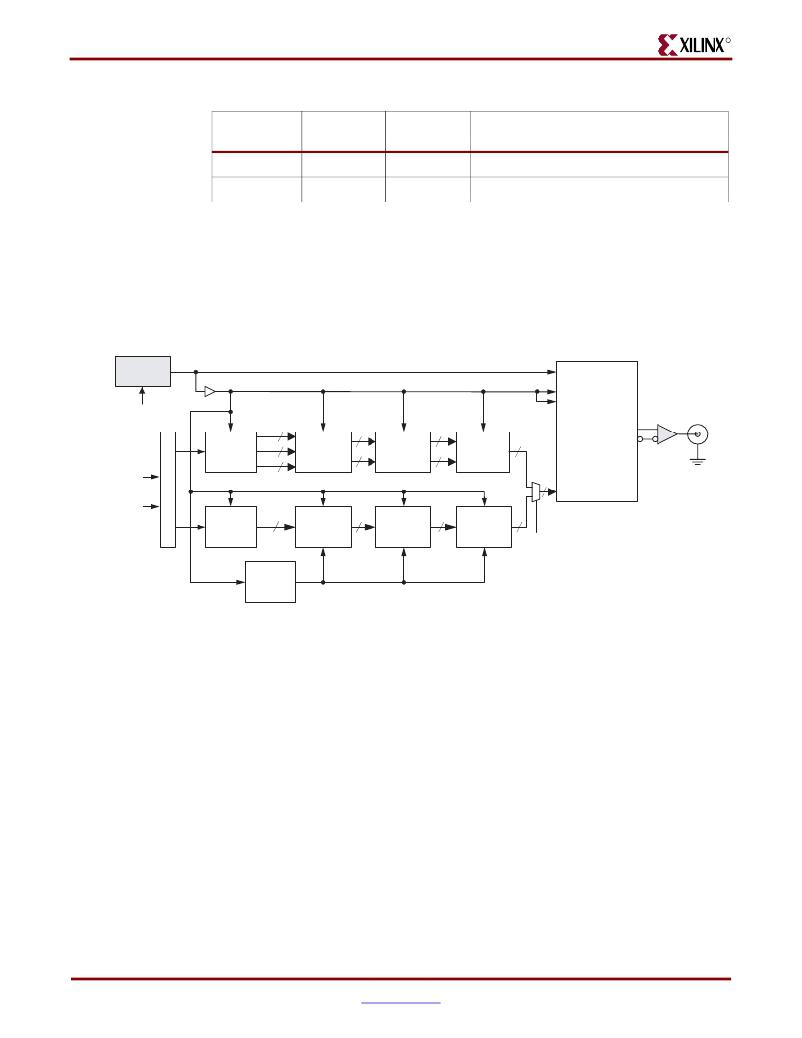

�Figure� 6-3� is� a� block� diagram� of� the� SDI� transmitter.� The� ICS664-02� frequency� synthesizer�

�provides� either� 74.25� MHz� or� 74.1758� MHz� in� HD� mode� or� 54� MHz� in� SD� mode.� This�

�reference� clock� is� connected� directly� to� the� REFCLK� input� of� the� RocketIO� transceiver� and�

�also� buffered� by� a� global� clock� buffer� and� distributed� as� the� transmitter� clock� to� all� portions�

�of� the� transmitter� section.�

�ICS664-02�

�BUFG�

�HD� mode:� 74.25� MHz� or74.1578� MHz�

�SD� mode:� 54� MHz�

�REFCLK�

�TXUSRCLK�

�freq� control�

�TXUSRCLK2�

�SDI� Cable�

�Driver� SDI� Out�

�Y�

�C�

�DIP�

�HD�

�Pattern�

�Generator�

�10�

�10�

�line� 11�

�num�

�Line�

�Number�

�Insertion�

�10�

�10�

�10�

�CRC�

�Insertion� 10�

�HD-SDI�

�Scrambler�

�20�

�TXP�

�TXN�

�RocketIO�

�switches�

�from�

�20�

�TXDATA�

�ML402�

�SD�

�Pattern�

�Generator�

�10�

�EDH�

�Processor�

�10�

�SD-SDI�

�Scrambler�

�10�

�4X� Bit�

�Replicate�

�20�

�hd_sd�

�Clock�

�Enable�

�Generator�

�ug235_ch5_03_111405�

�Figure� 6-3:� SDI� Transmitter� Block� Diagram�

�The� HD� pattern� generator� produces� four� different� video� patterns� for� each� of� the� eight� HD�

�video� formats� supported.� The� video� pattern� and� format� is� selected� either� by� the� DIP�

�switches� on� the� VIODC� or� by� the� ML402� board.� The� HD� pattern� generator� also� produces�

�an� 11-bit� line� number� value.� The� line� number� is� inserted� into� the� video� stream� after� each�

�End� of� Active� Video� (EAV)� by� the� line� number� insertion� logic.� The� Cyclic� Redundancy�

�Check� (CRC)� block� generates� CRCs� for� both� the� Y� and� C� channels� and� inserts� them� into� the�

�video� stream� after� the� line� number.� Finally,� the� video� is� encoded� for� transmission� by� the�

�HD-SDI� scrambler� and� provided� to� the� RocketIO� transceiver� where� it� is� serialized� and� sent�

�as� an� HD-SDI� bitstream.�

�In� SD� mode,� the� clock� from� the� ICS664-02� runs� at� 54� MHz.� This� is� supplied� to� the� RocketIO�

�transceiver� where� it� is� multiplied� by� 20,� so� that� the� actual� data� rate� of� the� transceiver� ’s�

�output� is� 1.08� Gb/s� or� 4X� the� 270� Mb/s� SD-SDI� bit� rate.� The� SD� pattern� generator� and� the�

�other� elements� of� the� SD-SDI� transmitter� data� path� need� to� run� at� 27� MHz,� so� a� clock�

�enable,� asserted� every� other� clock� cycle,� is� generated� and� distributed� to� all� elements� of� the�

�SD-SDI� transmitter� data� path.�

�The� SD� pattern� generator� produces� either� National� Television� System� Committee� (NTSC)� or�

�Phase� Alternating� Line� (PAL)� component� 4:2:2� video.� The� EDH� processor� calculates� the�

�48�

��Video� Input/Output� Daughter� Card�

�UG235� (v1.2.1)� October� 31,� 2007�

�相关PDF资料 |

PDF描述 |

|---|---|

| ICD15S13E6GV00LF | CONN DSUB HD SOCKT 15POS R/A PCB |

| ICD26S13E4GX00LF | CONN DSUB HD SOCKT 26POS R/A PCB |

| ID09S33E4GV00LF | CONN RCPT 9POS R/A GOLD |

| ID451000 | CONN RECPT USB A ADAPTER |

| IELHK11-1-72-70.0-01-V | CIRCUIT BREAKER HYMAG DP 70A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HWXX35338TR | 制造商:Vishay Intertechnologies 功能描述: |

| HWXX38438 | 制造商:Vishay Semiconductors 功能描述: |

| HWZ1408 | 制造商:OHIO BUCKEYE 功能描述: |

| HWZ1424 | 制造商:OHIO BUCKEYE 功能描述: |

| HWZ1620 | 制造商:OHIO BUCKEYE 功能描述: |

发布紧急采购,3分钟左右您将得到回复。