- 您现在的位置:买卖IC网 > PDF目录359091 > M68HC705UGANG (飞思卡尔半导体(中国)有限公司) High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit PDF资料下载

参数资料

| 型号: | M68HC705UGANG |

| 厂商: | 飞思卡尔半导体(中国)有限公司 |

| 英文描述: | High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| 中文描述: | 高密度互补金属氧化物半导体(HCMOS)微控制器 |

| 文件页数: | 24/112页 |

| 文件大小: | 809K |

| 代理商: | M68HC705UGANG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页

2-4

MC68HC05BD3

PIN DESCRIPTION AND I/O PORTS

2

2.3.3

Port C

Port C is an 8-bit bidirectional port which shares pins with PWM and SSP subsystem. See

Section 6 for a detailed description of PWM and Section 8 for a detailed description of SSP. These

pins are configured to PWM output when the corresponding bits in the Configuration register 1 are

set, except PC6 and PC7. PC6 and PC7 are configured to SSP outputs when the corresponding

bits in the Configuration register 2 are set. The Port C data register is at $02 and the data direction

register (DDR) is at $06. Reset does not affect the data register, but clears the data direction

register, thereby returning the ports to inputs. Writing a one to a DDR bit sets the corresponding

port bit to output mode.

2.3.4

Port D

Port D is a 2-bit bidirectional port which shares pins with M-Bus subsystem. See Section 7 for a

detailed description of M-Bus. These pins are configured to the corresponding functions when the

corresponding bits in the Configuration register 2 are set. They are +5V open-drain I/O pins when

used as M-Bus I/O. The Port D data register is at $03 and the data direction register (DDR) is at

$07. Reset does not affect the data register, yet clears the data direction register, thereby returning

the ports to inputs. Writing a one to a DDR bit sets the corresponding port bit to output mode.

2.3.5

Input/Output Programming

Bidirectional port lines may be programmed as an input or an output under software control. The

direction of the pins is determined by the state of the corresponding bit in the port data direction

register (DDR). Each port has an associated DDR. Any I/O port pin is configured as an output if

its corresponding DDR bit is set. A pin is configured as an input if its corresponding DDR bit is

cleared.

During Reset, all DDRs are cleared, which configure all port pins as inputs. The data direction

registers are capable of being written to or read by the processor. During the programmed output

state, a read of the data register actually reads the value of the output data latch and not the I/O

pin.

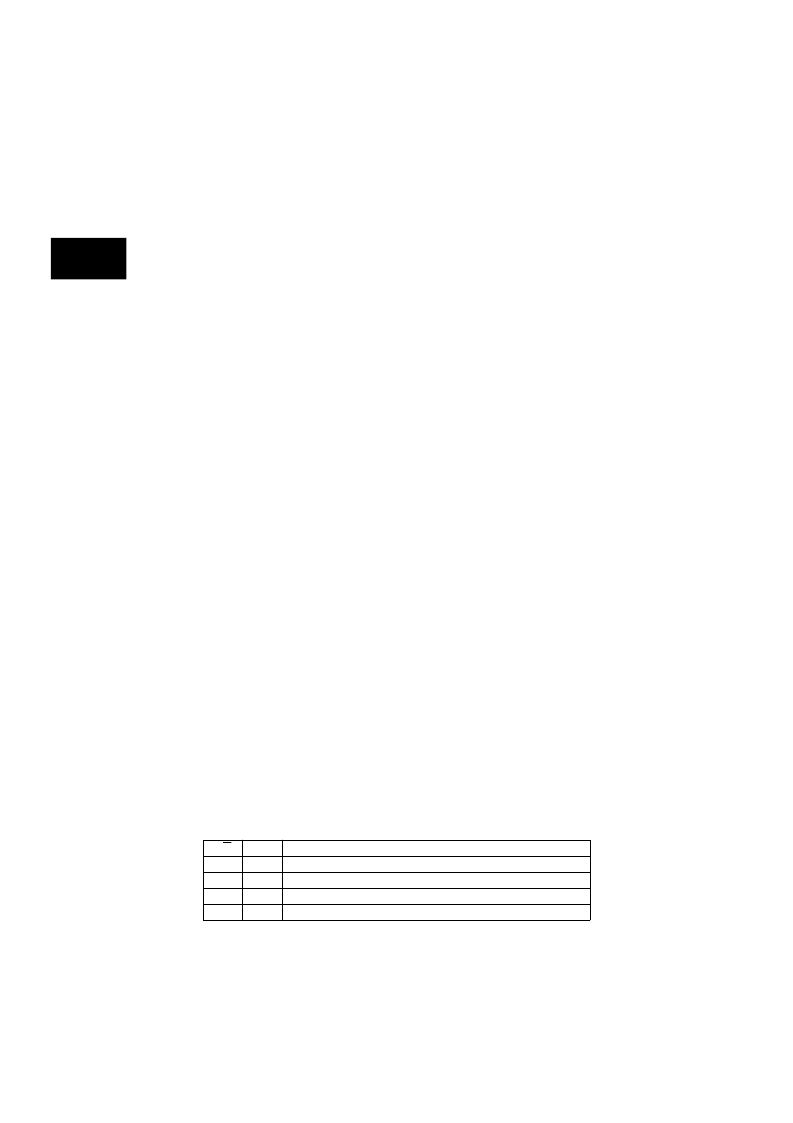

Table 2-1

I/O Pin Functions

R/W

0

0

1

1

DDR

0

1

0

1

I/O Pin Function

The I/O pin is in input mode. Data is written into the output data latch.

Data is written into the output data latch and output to the I/O pin.

The state of the I/O pin is read.

The I/O pin is in an output mode. The output data latch is read.

TPG

22

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相关PDF资料 |

PDF描述 |

|---|---|

| M68TC11E20B56 | HC11 Microcontrollers |

| M68Z128W-70N1T | 3V, 1 Mbit 128Kb x8 Low Power SRAM with Output Enable |

| M68Z128WN | 3V, 1 Mbit 128Kb x8 Low Power SRAM with Output Enable |

| M68Z128W | 3V, 1 Mbit 128Kb x8 Low Power SRAM with Output Enable |

| M69AW024BL60ZB8T | 16 Mbit (1M x16) 3V Asynchronous PSRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M68HC705UPGMR | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705X16PGMR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| M68HC711CFD | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

| M68HC711CFG | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

| M68HC711CFG/D | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

发布紧急采购,3分钟左右您将得到回复。