- 您现在的位置:买卖IC网 > PDF目录262949 > MT45W2MV16BAFB-706LIT 2M X 16 PSEUDO STATIC RAM, 70 ns, PBGA54 PDF资料下载

参数资料

| 型号: | MT45W2MV16BAFB-706LIT |

| 元件分类: | SRAM |

| 英文描述: | 2M X 16 PSEUDO STATIC RAM, 70 ns, PBGA54 |

| 封装: | FBGA-54 |

| 文件页数: | 11/55页 |

| 文件大小: | 816K |

| 代理商: | MT45W2MV16BAFB-706LIT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

2 MEG x 16

ASYNC/PAGE/BURST CellularRAM MEMORY

ADVANCE

09005aef80ec6f63

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Burst CellularRAM_32.fm - Rev. A 2/18/04 EN

19

2004 Micron Technology, Inc. All Rights Reserved.

WAIT Configuration (BCR[8])

Default = WAIT Transitions One Clock

Before Data Valid/Invalid

The WAIT configuration bit is used to determine

when WAIT transitions between the asserted and the

de-asserted state with respect to valid data presented on

the data bus. The memory controller will use the WAIT

signal to coordinate data transfer during synchronous

READ and WRITE operations. When BCR[8] = 0, data

will be valid or invalid on the clock edge immediately

after WAIT transitions to the de-asserted or asserted

WAIT signal transitions one clock period prior to the

data bus going valid or invalid (Figures 17 and 16).

WAIT Polarity (BCR[10])

Default = WAIT Active HIGH

The WAIT polarity bit indicates whether an asserted

WAIT output should be HIGH or LOW. This bit will

determine whether the WAIT signal requires a pull-up

or pull-down resistor to maintain the de-asserted

state.

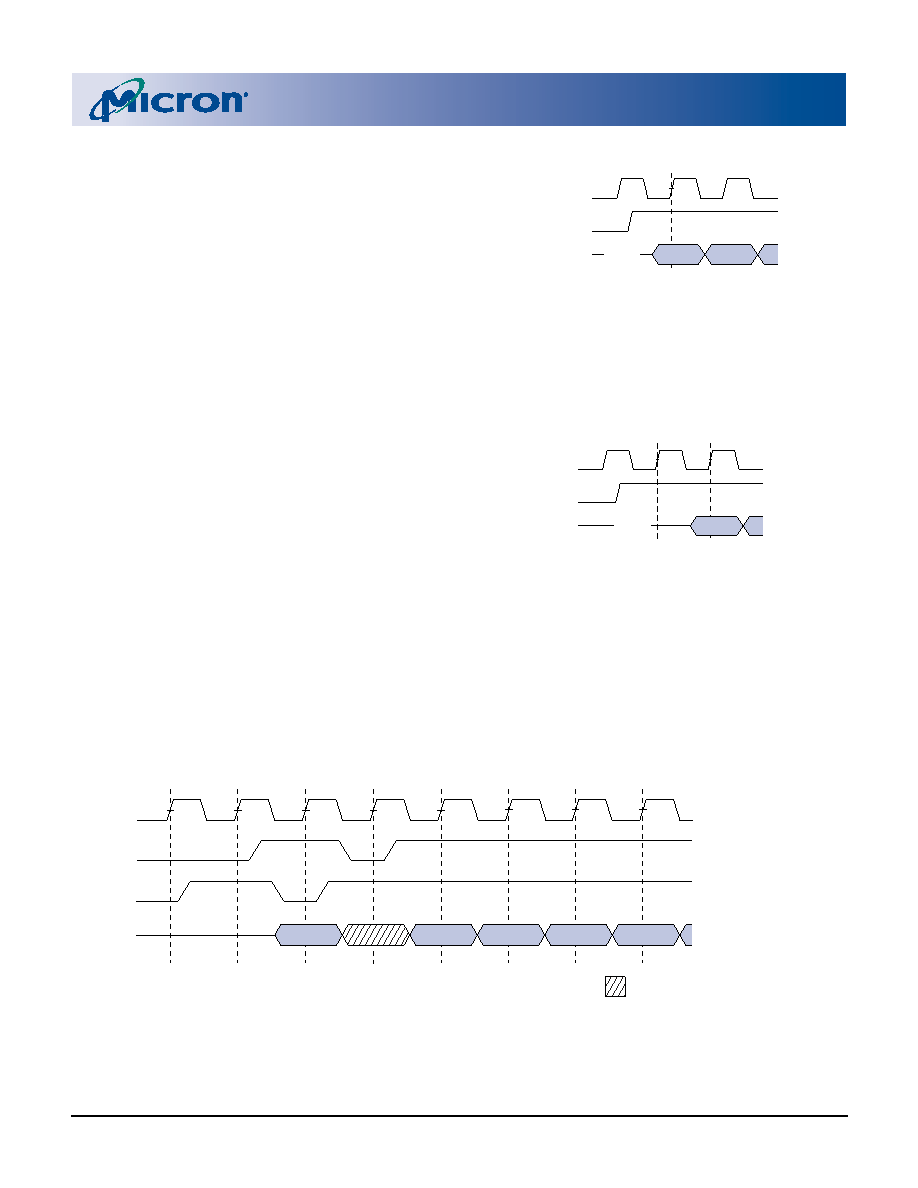

Figure 16: WAIT Configuration (BCR[8] = 0)

NOTE:

1. Note: Data valid/invalid immediately after WAIT

transitions (BCR[8] = 0). See Figure 18.

Figure 17: WAIT Configuration (BCR[8] = 1)

NOTE:

1. Note: Valid/invalid data delayed for one clock after

WAIT transitions (BCR[8] = 1). See Figure 18.

Figure 18: WAIT Configuration During Burst Operation1

NOTE:

1. Non-default BCR setting: WAIT active LOW.

WAIT

DQ[15:0]

CLK

Data[0]

Data[1]

Data immediately valid (or invalid)

High-Z

WAIT

D[15:0]

CLK

Data[0]

Data valid (or invalid) after one clock delay

High-Z

WAIT

DQ[15:0]

CLK

D[0]

D[1]

BCR[8] = 0

DATA VALID IN CURRENT CYCLE

BCR[8] = 1

DATA VALID IN NEXT CYCLE

DON’T CARE

D[2]

D[3]

D[4]

相关PDF资料 |

PDF描述 |

|---|---|

| MT28C128532W30EBW-F705P856BTWT | SPECIALTY MEMORY CIRCUIT, PBGA77 |

| M93C66-MB6TP | 256 X 16 MICROWIRE BUS SERIAL EEPROM, DSO8 |

| MT48V8M16LFB4-75M:G | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

| MS8256FKXA-12 | 256K X 8 MULTI DEVICE SRAM MODULE, 120 ns, DMA32 |

| MT46V32M16BN-75IT | 32M X 16 DDR DRAM, 0.75 ns, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT45W2MV16PFA-70 WT | 制造商:Micron Technology Inc 功能描述:2MX16 PSRAM PLASTIC WIRELESS TEMP FBGA 1.8V ASYNCH PSEUDO ST - Trays |

| MT45W2MW16BABB-706 L WT | 功能描述:IC PSRAM 32MBIT 70NS 54VFBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:378 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:8M(1M x 8,512K x 16) 速度:110ns 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-CBGA 供应商设备封装:48-CBGA(7x7) 包装:托盘 |

| MT45W2MW16BABB-706 L WT TR | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS 54VFBGA - Tape and Reel |

| MT45W2MW16BABB-706 WT | 制造商:Micron Technology Inc 功能描述:PSRAM Async 1 32M-Bit 2M x 16 70ns 54-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS 54VFBGA - Trays 制造商:Micron Technology Inc 功能描述:IC PSRAM 32MBIT 70NS 54VFBGA |

| MT45W2MW16BABB-706 WT TR | 功能描述:IC PSRAM 32MBIT 70NS 54VFBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:96 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:16M(2M x 8,1M x 16) 速度:70ns 接口:并联 电源电压:2.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。