- 您现在的位置:买卖IC网 > PDF目录299581 > ORT82G5-2BM680 (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 380000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | ORT82G5-2BM680 |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| 封装: | PLASTIC, BGA-680 |

| 文件页数: | 32/110页 |

| 文件大小: | 1459K |

| 代理商: | ORT82G5-2BM680 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

28

Lattice Semiconductor

Data Sheet

January 25, 2002

8b/10b SERDES Backplane Interface FPSC

ORCA ORT82G5 1.0-1.25/2.0-2.5/3.125-3.5 Gbits/s

Backplane Transceiver Core Detailed

Description (continued)

Receive Path (Backplane → FPGA)

The deMUX has to accumulate four sets of characters

presented to it at the SERDES receive interface and

put these out at one time at the low-speed receive

interface.

Another task of the deMUX is to recognize the synchro-

nizing event and adjust the 4-byte boundary so that the

synchronizing character leads off a new 4-byte word.

Typically, this synchronizing character is a comma.

This feature will be referred to as deMUX word align-

ment in other areas of this document. DeMUX word

alignment will only occur when the communication

channel is synchronized. When there is no synchroni-

zation of the link, the deMUX will continue to output 4-

byte words at some arbitrary, but constant, boundary.

There are 2 controls available to each channel for word

alignment. They are DOWDALGN and NOWDALGN.

The DOWDALGN bit is positive edge triggered. Writing

a 0 followed by a 1 to this register bit will cause the

deMUX to look for a new comma character and align

the 32-bit word such that the comma is in the most sig-

nicant byte position. It is important that the comma is

in the most signicant byte position since the multi-

channel aligner looks for comma in the most signicant

byte only. Typically, it is not necessary to set the

DOWDALGN bit. When the link state machine loses

synchronization (DEMUXWAS register bit is 0), the

deMUX block automatically looks for a new comma

character irrespective of whether the DOWDALGN bit

is set or not. A scenario where the DOWDALGN bit can

be set is when no channel alignment happens for

sometime and one of the reasons could be that there is

no comma character in the most signicant byte posi-

tion. There can be a loss of data from creating a new

word boundary based on a comma.

The NOWDALGN bit is a level-sensitive bit. If it is a 1,

then the deMUX does not dynamically alter the word

boundary based on comma and SWDSYNCx output of

the SERDES. This might be useful if a channel were

congured to bypass the multi-channel alignment FIFO

and raw 40-bits of data are directed from SERDES to

FPGA. The default (NOWDALGN = 0) causes the word

boundary to be set as soon as the SERDES

SWDSYNCx output is a 1 and a comma character has

been detected. The character that is the comma

becomes the most-signicant portion of the demulti-

plexed word. When the SERDES loses link synchroni-

zation it will drop SWDSYNCx low. The deMUX will

begin search for word alignment as soon as

SWDSYNCx goes to 1 again.

The deMUX passes on to the channel alignment FIFO

block a set of control signals that indicate the location

of the synchronizing event. RCOMMAx[3:0] are these

indicators. If there is no link synchronization, all of the

RCOMMAx[3:0] bits will be 0s independent of synchro-

nizing events that come in. When the link is synchro-

nized, then the bit that corresponds to the time of the

synchronization event will be set to a 1.

The relationship between a time sequence of values

input at SRBDx[7:0] to the values output at

RWDx[31:0] is shown in Figure 9 below. A parallel rela-

tionship exists between SRBDx[8] and RWBIT8x[3:0]

as well as between SRBDx[9] and RWBIT9x[3:0].

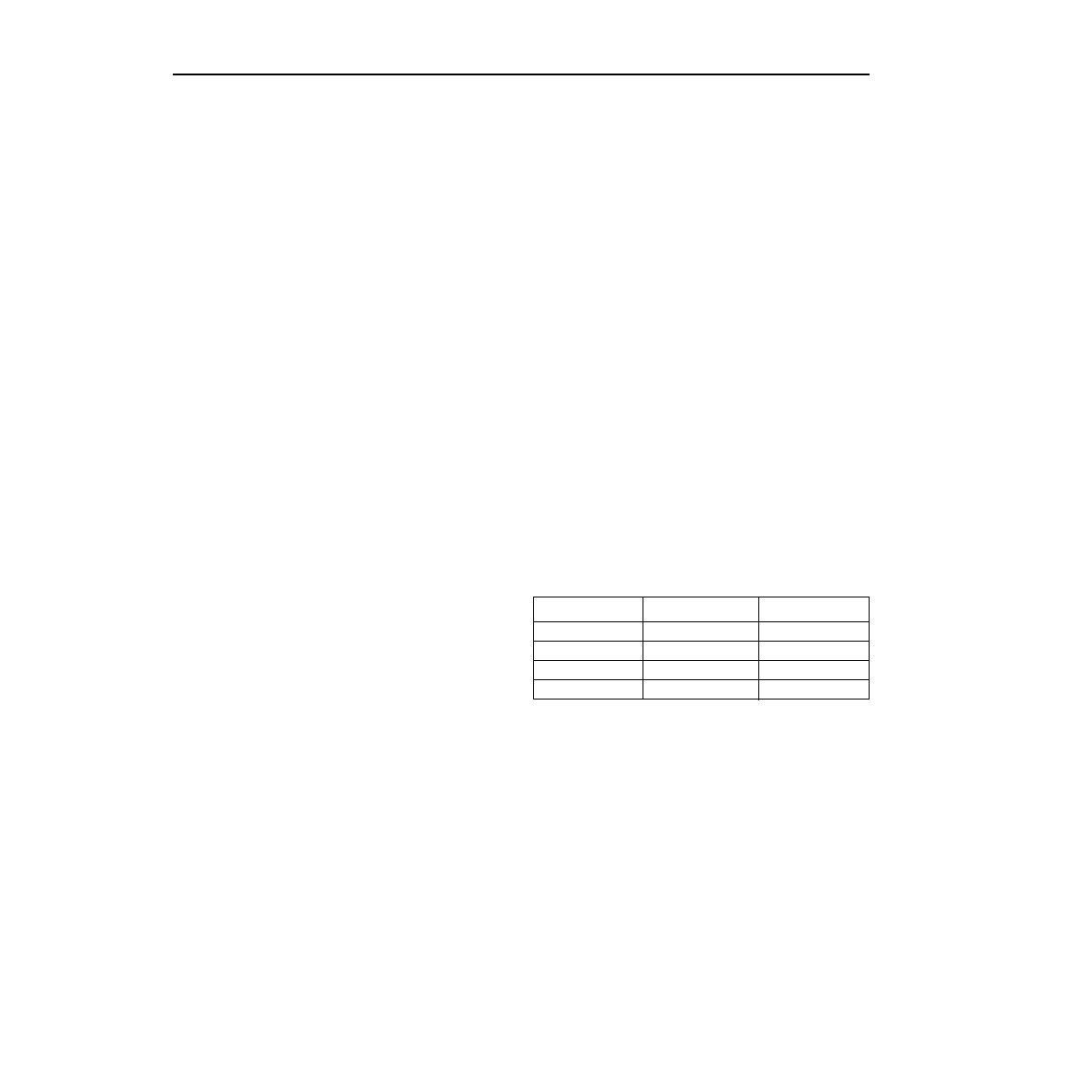

One clock per bank of 4 channels called RCK78(A,B) is

sent to the FPGA. The control bits RCKSEL(A,B) are

used to select the clock source for these clocks. The

selection of clock source for RCK78(A,B) is shown in

Table 9. RCK78 Selection

RCKSEL0

RCKSEL1

Clock Source

00

Channel A

10

Channel B

01

Channel C

11

Channel D

相关PDF资料 |

PDF描述 |

|---|---|

| ORT82G5-3BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| OS10040280G-012 | FIBER OPTIC RECEIVER, 1290-1600nm, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-10-X-9-M-3-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 10.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-13-9-F-1-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-X-9-O-1-99-SA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, SC/APC CONNECTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ORT82G5-2BM680C | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2BM680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2F680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2F680I | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 2.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2FN680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。