- 您现在的位置:买卖IC网 > PDF目录299581 > ORT82G5-2BM680 (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 380000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | ORT82G5-2BM680 |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| 封装: | PLASTIC, BGA-680 |

| 文件页数: | 55/110页 |

| 文件大小: | 1459K |

| 代理商: | ORT82G5-2BM680 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

Lattice Semiconductor

49

Data Sheet

January 25, 2002

8b/10b SERDES Backplane Interface FPSC

ORCA ORT82G5 1.0-1.25/2.0-2.5/3.125-3.5 Gbits/s

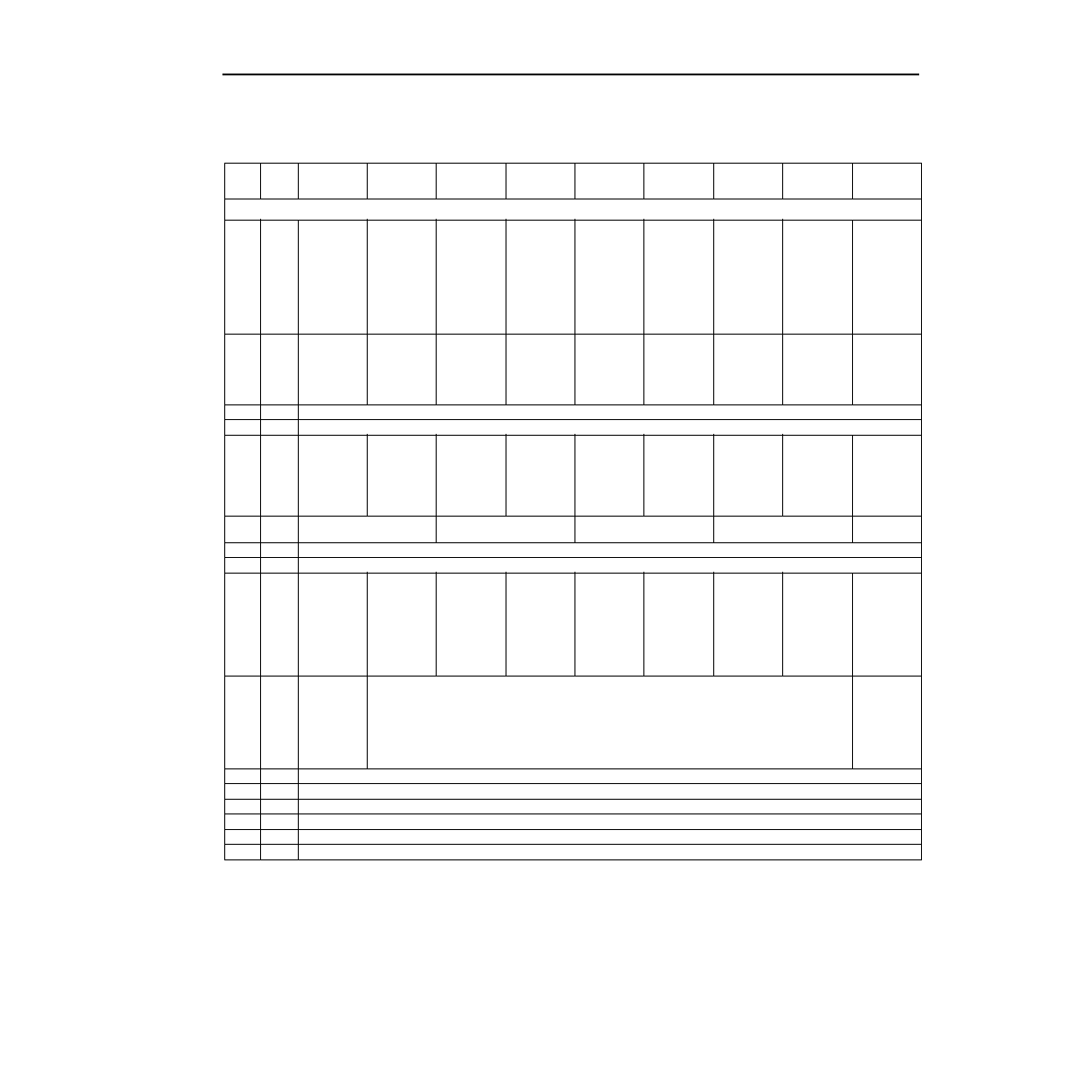

Memory Map (continued)

Table 18. Memory Map (continued)

* FMPU_SYNMODE_xx[0:1]

00 = No channel alignment

10 = Twin channel alignment

01 = Quad channel alignment

11 = 8 channel alignment

Addr

(Hex)

Reg

#

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

Default

Value

Control Registers A

30800

A0

ENBYSYNC_

AA

1 = Byte

Alignments

bank A, chan-

nelA

ENBYSYNC_

AB

1 = Byte

Alignments

bank A, chan-

nel B

ENBYSYNC_

AC

1 = Byte

Alignments

bank A, chan-

nel C

ENBYSYNC_

AD

1 = Byte

Alignments

bank A, chan-

nel D

LCKREFN_A

A

0 = Lock

receiver to

ref. clock

1 = Lock

receiver to

data

for bank A

channel A

LCKREFN_A

B

0 =Lock

receiver to

ref. clock

1 =Lock

receiver to

data

for bank A

channel B

LCKREFN_A

C

0 = Lock

receiver to

ref. clock

1 = Lock

receiver to

data

for bank A

channel C

LCKREFN_A

D

0 = Lock

receiver to

ref. clock

1 = Lock

receiver to

data

for bank A

channel D

00

30801

A1

LOOPENB_A

A

Enable loop-

back mode for

bank A, chan-

nel A

LOOPENB_A

B

Enable loop-

back mode for

bank A, chan-

nel B

LOOPENB_A

C

Enable loop-

back mode for

bank A, chan-

nel C

LOOPENB_A

D

Enable loop-

back mode for

bank A, chan-

nel D

NOWDALIGN

_AA

Defeats

deMUX align-

ment for bank

A, channel A

NOWDALIGN

_AB

Defeats

deMUX align-

ment for bank

A, channel B

NOWDALIGN

_AC

Defeats

deMUX align-

ment for bank

A, channel C

NOWDALIGN

_AD

Defeats

deMUX align-

ment for bank

A, channel

00

30802

A2

Reserved for future use

30803

A3

Reserved for future use

30810

A4

DOWDALIGN

_AA

Force new

deMUX word

alignment for

bank A, chan-

nel A

DOWDALIGN

_AB

Force new

deMUX word

alignment for

bank A, chan-

nel B

DOWDALIGN

_AC

Force new

deMUX word

alignment for

bank A, chan-

nel C

DOWDALIGN

_AD

Force new

deMUX word

alignment for

bank A, chan-

nel D

FMPU_STR_

EN _AA

Enable align-

ment function

for channel

AA

FMPU_STR_

EN _AB

Enable align-

ment function

for channel

AB

FMPU_STR_

EN_AC

Enable align-

ment function

for channel

AC

FMPU_STR_

EN_AD

Enable align-

ment function

for channel

AD

00

30811

A5*

FMPU_SYNMODE_AA[0:1]

Sync mode for AA

FMPU_SYNMODE_AB[0:1]

Sync mode for AB

FMPU_SYNMODE_AC[0:1]

Sync mode for AC

FMPU_SYNMODE_AD[0:1]

Sync mode for AD

00

30812

A6

Reserved for future use

30813

A7

Reserved for future use

30820

A8

FMPU_RESY

NC1_AA

Resync a sin-

gle channel,

AA.

Write a 0,

then write a 1.

FMPU_RESY

NC1_AB

Resync a sin-

gle channel,

AB.

Write a 0,

then write a 1.

FMPU_RESY

NC1_AC

Resync a sin-

gle channel,

AC.

Write a 0,

then write a 1.

FMPU_RESY

NC1_AD

Resync a sin-

gle channel,

AD.

Write a 0,

then write a 1.

FMPU_RESY

NC2_A1

Resync 2

channels, AA

and AB.

Write a 0,

then write a 1.

FMPU_RESY

NC2A2

Resync 2

channels, AC

and AD.

Write a 0,

then write a 1.

FMPU_RESY

NC4A

Resync 4

channels

A[A:D].

Write a 0,

then write a 1.

XAUI_MODE

A

Controls use

of XAUI link

state machine

vs. SERDES

link State

machine for

bank A

00

30821

A9

NOCHALGN

A

Bypass chan-

nel alignment

deMUXed

data directly

to FPGA for

bank A

Reserved for future use

00

30822

A10

Reserved for future use

30823

A11

Reserved for future use

30830

A12

Reserved for future use

30831

A13

Reserved for future use

30832

A14

Reserved for future use

30833

A15

Reserved for future use

相关PDF资料 |

PDF描述 |

|---|---|

| ORT82G5-3BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| OS10040280G-012 | FIBER OPTIC RECEIVER, 1290-1600nm, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-10-X-9-M-3-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 10.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-13-9-F-1-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-X-9-O-1-99-SA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, SC/APC CONNECTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ORT82G5-2BM680C | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2BM680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2F680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2F680I | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 2.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORT82G5-2FN680C | 功能描述:FPGA - 现场可编程门阵列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。