- 您现在的位置:买卖IC网 > Datasheet目录369 > W9725G6JB25I (Winbond Electronics)IC DDR2 SDRAM 256MBIT 84WBGA Datasheet资料下载

参数资料

| 型号: | W9725G6JB25I |

| 厂商: | Winbond Electronics |

| 文件页数: | 49/87页 |

| 文件大小: | 0K |

| 描述: | IC DDR2 SDRAM 256MBIT 84WBGA |

| 标准包装: | 200 |

| 格式 - 存储器: | RAM |

| 存储器类型: | DDR2 SDRAM |

| 存储容量: | 256M(16Mx16) |

| 速度: | 2.5ns |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | -40°C ~ 95°C |

| 封装/外壳: | 84-TFBGA |

| 供应商设备封装: | 84-WBGA(8x12.5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

�� �

�

�

�W9725G6JB�

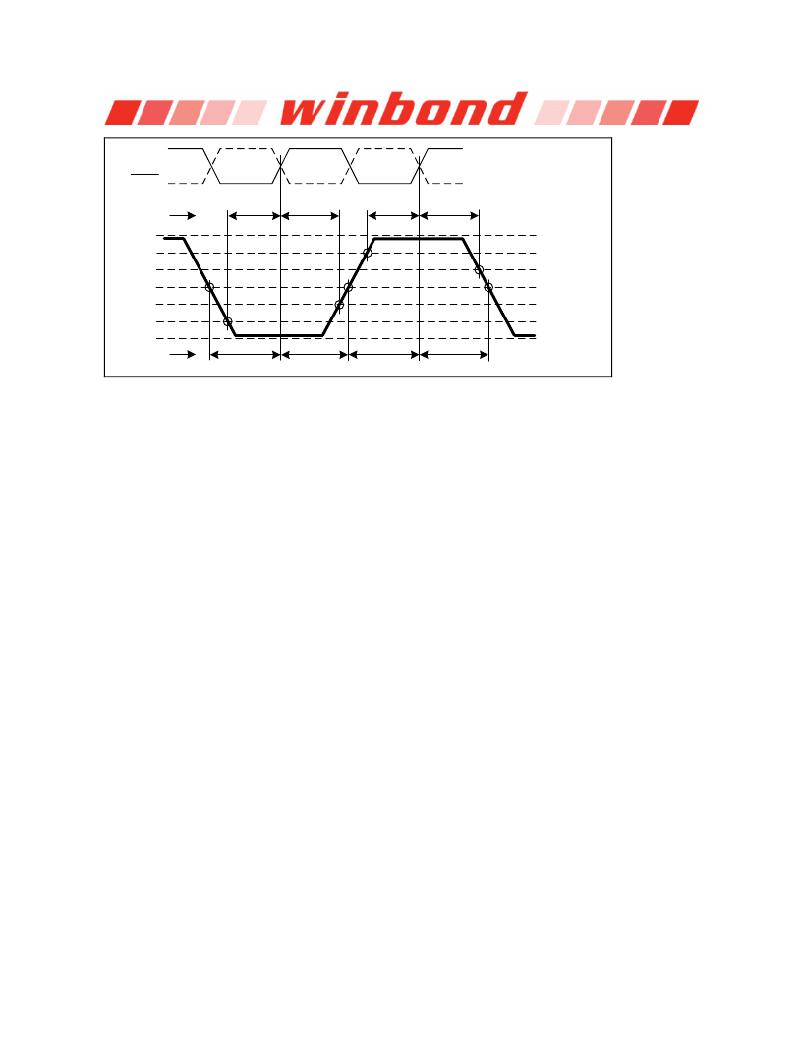

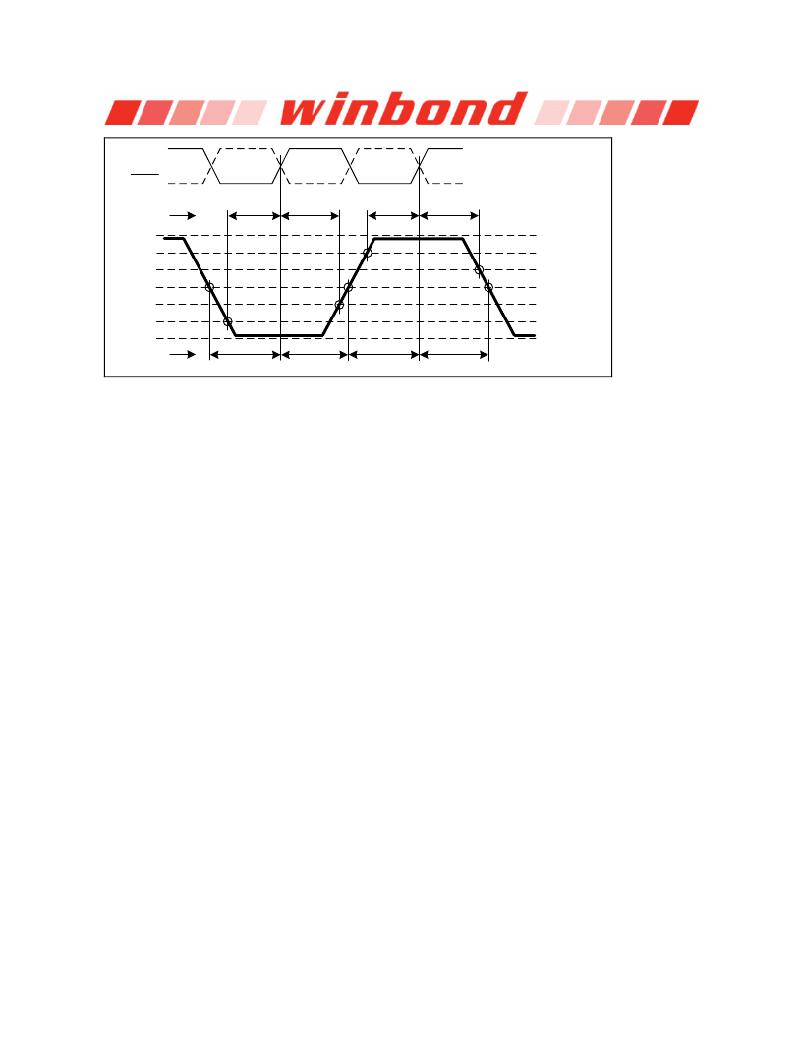

�DQS�

�DQS�

�t� DS(base)� t� DH(base)�

�t� DS(base)� t� DH(base)�

�Logic� levels�

�V� DDQ�

�V� IH(ac)� min�

�V� IH(dc)� min�

�V� REF(dc)�

�V� IL(dc)� max�

�V� IL(ac)� max�

�V� SS�

�V� REF� levels�

�t� DS(ref)�

�t� DH(ref)�

�t� DS(ref)�

�t� DH(ref)�

�Figure� 19�

�–� Differential� input� waveform� timing� –� tDS� and� tDH�

�18.� User� can� choose� which� active� power� down� exit� timing� to� use� via� MRS� (bit� 12).� tXARD� is� expected� to� be� used� for� fast� active�

�power� down� exit� timing.� tXARDS� is� expected� to� be� used� for� slow� active� power� down� exit� timing.�

�19.� AL� =� Additive� Latency.�

�20.� ODT� turn� on� time� min� is� when� the� device� leaves� high� impedance� and� ODT� resistance� begins� to� turn� on.� ODT� turn� on� time�

�max� is� when� the� ODT� resistance� is� fully� on.� Both� are� measure� from� tAOND,� which� is� interpreted� differently� per� speed� bin.�

�For� DDR2-667/800/1066,� tAOND� is� 2� clock� cycles� after� the� clock� edge� that� registered� a� first� ODT� HIGH� counting� the� actual�

�input� clock� edges.�

�21.� ODT� turn� off� time� min� is� when� the� device� starts� to� turn� off� ODT� resistance.� ODT� turn� off� time� max� is� when� the� bus� is� in� high�

�impedance.� Both� are� measured� from� tAOFD,� which� is� interpreted� as� 0.5� x� tCK(avg)� [nS]� after� the� second� trailing� clock� edge�

�counting� from� the� clock� edge� that� registered� a� first� ODT� LOW� and� by� counting� the� actual� input� clock� edges.�

�For� DDR2-667/800:� If� tCK(avg)� =� 3� nS� is� assumed,� tAOFD� is� 1.5� nS� (=� 0.5� x� 3� nS)� after� the� second� trailing� clock�

�edge� counting� from� the� clock� edge� that� registered� a� first� ODT� LOW� and� by� counting� the� actual� input� clock� edges.�

�For� DDR2-1066:� tAOFD� is� 0.9375� [nS]� (=� 0.5� x� 1.875� [nS])� after� the� second� trailing� clock� edge� counting� from� the�

�clock� edge� that� registered� a� first� ODT� LOW� and� by� counting� the� actual� input� clock� edges.�

�22.� The� clock� frequency� is� allowed� to� change� during� Self� Refresh� mode� or� precharge� power-down� mode.� In� case� of� clock�

�frequency� change� during� precharge� power-down,� a� specific� procedure� is� required� as� described� in� section� 7.10.�

�23.� For� these� parameters,� the� DDR2� SDRAM� device� is� characterized� and� verified� to� support� tnPARAM� =� RU{tPARAM� /�

�tCK(avg)},� which� is� in� clock� cycles,� assuming� all� input� clock� jitter� specifications� are� satisfied.�

�Examples:�

�The� device� will� support� tnRP� =� RU{tRP� /� tCK(avg)},� which� is� in� clock� cycles,� if� all� input� clock� jitter� specifications� are�

�met.� This� means:� For� DDR2-667� 5-5-5,� of� which� tRP� =� 15nS,� the� device� will� support� tnRP� =� RU{tRP� /� tCK(avg)}� =� 5,�

�i.e.� as� long� as� the� input� clock� jitter� specifications� are� met,� Precharge� command� at� Tm� and� Active� command� at� Tm+5�

�is� valid� even� if� (Tm+5� -� Tm)� is� less� than� 15nS� due� to� input� clock� jitter.� For� DDR2-1066� 7-7-7,� of� which� tRP� =� 13.125�

�nS,� the� device� will� support� tnRP� =� RU{tRP� /� tCK(avg)}� =� 7,� i.e.� as� long� as� the� input� clock� jitter� specifications� are� met,�

�Precharge� command� at� Tm� and� Active� command� at� Tm+7� is� valid� even� if� (Tm+7� -� Tm)� is� less� than� 13.125� nS� due� to�

�input� clock� jitter.�

�24.� tDAL� [nCK]� =� WR� [nCK]� +� tnRP� [nCK]� =� WR� +� RU� {tRP� [pS]� /� tCK(avg)� [pS]� },� where� WR� is� the� value� programmed� in� the�

�mode� register� set� and� RU� stands� for� round� up.�

�Example:�

�For� DDR2-1066� 7-7-7� at� tCK(avg)� =� 1.875� nS� with� WR� programmed� to� 8� nCK,� tDAL� =� 8� +� RU{13.125� nS� /� 1.875�

�nS}� [nCK]� =� 8� +� 7� [nCK]� =� 15� [nCK].�

�Publication� Release� Date:� Nov.� 29,� 2011�

�-� 49� -�

�Revision� A02�

�相关PDF资料 |

PDF描述 |

|---|---|

| W9725G6KB-25I | IC DDR2 SDRAM 256MBIT 84WBGA |

| W972GG6JB-3I | IC DDR2 SDRAM 2GBITS 84WBGA |

| W9751G6IB-25 | IC DDR2-800 SDRAM 512MB 84-WBGA |

| W9751G6KB-25 | IC DDR2 SDRAM 512MBIT 84WBGA |

| W9812G6JH-6I | IC SDRAM 128MBIT 54TSOPII |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G6KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G6KB-25 | 功能描述:IC DDR2 SDRAM 256MBIT 84WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:4G(256M x 16) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP I 包装:Digi-Reel® 其它名称:557-1461-6 |

| W9725G6KB-25 TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X16 |

| W9725G6KB25A | 制造商:WINBOND 制造商全称:Winbond 功能描述:DLL aligns DQ and DQS transitions with clock, Data masks (DM) for write data, Write Data Mask |

| W9725G6KB25I | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin WBGA 制造商:Winbond Electronics 功能描述:IC DDR2 SDRAM 256M 2.5NS 84WBGA 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 256M 2.5NS 84WBGA 制造商:Winbond 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin WBGA |

发布紧急采购,3分钟左右您将得到回复。