参数资料

| 型号: | AD9557BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/92页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK TRANSLATOR 40LFCSP |

| 产品变化通告: | Minor Mask Change 11/Apr/2012 |

| 标准包装: | 1 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

AD9557

Data Sheet

Rev. B | Page 30 of 92

In the automatic modes, a fully automatic priority-based algorithm

selects which reference is the active reference. When programmed

for an automatic mode, the device chooses the highest priority

valid reference. When both references have the same priority,

REFA gets preference over REFB. However, the reference position

is used only as a tie-breaker and does not initiate a reference switch.

The following list gives an overview of the five operating modes:

Automatic revertive mode. The device selects the highest

priority valid reference and switches to a higher priority

reference if it becomes available, even if the reference in use

is still valid. In this mode, the user reference is ignored.

Automatic non-revertive mode. The device stays with the

currently selected reference as long as it is valid, even if

a higher priority reference becomes available. The user

reference is ignored in this mode.

Manual with automatic fallback mode. The device uses the

user reference for as long as it is valid. If it becomes invalid,

the reference input with the highest priority is chosen in

accordance with the priority-based algorithm.

Manual with holdover mode. The user reference is the

active reference until it becomes invalid. At that point,

the device automatically goes into holdover.

Manual mode without holdover. The user reference is the

active reference, regardless of whether or not it is valid.

The user also has the option to force the device directly into

holdover or free run operation via the user holdover and user

freerun bits. In free run mode, the free run frequency tuning

word register defines the free run output frequency. In holdover

mode, the output frequency depends on the holdover control

settings (see the Holdover section).

Phase Build-Out Reference Switching

The AD9557 supports phase build-out reference switching,

which is the term given to a reference switchover that completely

masks any phase difference between the previous reference and

the new reference. That is, there is virtually no phase change

detectable at the output when a phase build-out switchover occurs.

DIGITAL PLL (DPLL) CORE

DPLL Overview

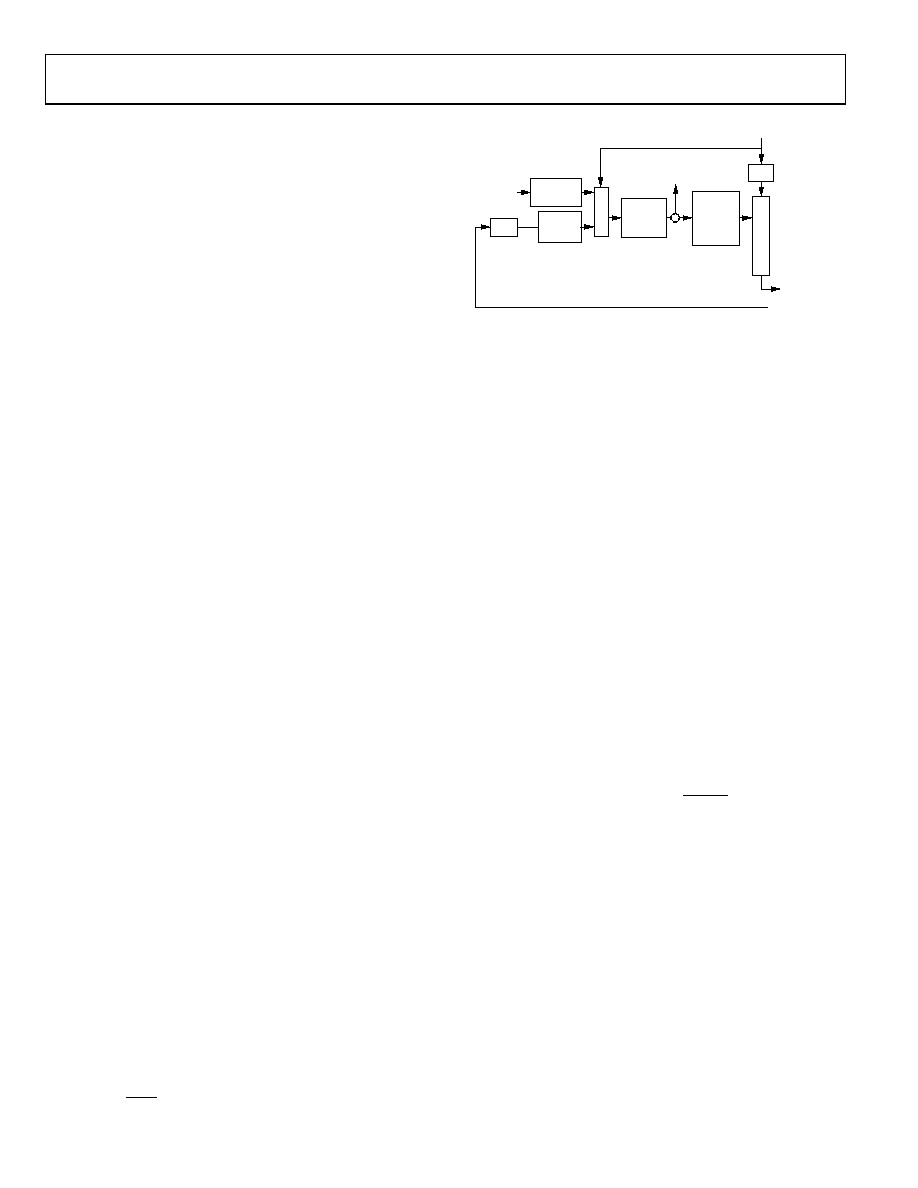

A diagram of the DPLL core of the AD9557 appears in Figure 36.

The phase/frequency detector, feedback path, lock detectors,

phase offset, and phase slew rate limiting that comprise this second

generation DPLL are all digital implementations.

The start of the DPLL signal chain is the reference signal, fR,

which is the frequency of the reference input. A reference prescaler

reduces the frequency of this signal by an integer factor, R + 1,

where R is the 20-bit value stored in the appropriate profile register

and 0 ≤ R ≤ 1,048,575. Therefore, the frequency at the output

of the R divider (or the input to the time-to-digital converter

(TDC)) is

1

+

=

R

f

R

TDC

DIGITAL

LOOP

FILTER

÷N1

R DIVIDER

(20-BIT)

24-BIT/24-BIT

RESOLUTION

FRAC1/

MOD1

17-BIT

INTEGER

TUNING

WORD

CLAMP

AND

HISTORY

×2

FREE RUN

TW

+

30-

BI

T

NCO

DP

F

D

SYSTEM

CLOCK

FROM APLL

FROM

REF

INPUT

MUX

TO APLL

09197-

136

Figure 36. Digital PLL Core

A TDC samples the output of the R divider. The TDC/PFD

produces a time series of digital words and delivers them to the

digital loop filter. The digital loop filter offers the following

advantages:

Determination of the filter response by numeric

coefficients rather than by discrete component values

The absence of analog components (R/L/C), which

eliminates tolerance variations due to aging

The absence of thermal noise associated with analog

components

The absence of control node leakage current associated

with analog components (a source of reference feed-

through spurs in the output spectrum of a traditional

analog PLL)

The digital loop filter produces a time series of digital words at

its output and delivers them to the frequency tuning input of

a sigma-delta (Σ-Δ) modulator (SDM). The digital words from

the loop filter steer the DCO frequency toward frequency and

phase lock with the input signal (fTDC).

The DPLL includes a feedback divider that causes the digital

loop to operate at an integer-plus-fractional multiple. The

output of the DPLL is

+

×

=

MOD1

FRAC1

N1

f

TDC

DPLL

OUT

)

1

(

_

where N1 is the 17-bit value stored in the appropriate profile

registers (Register 0x0715 to Register 0x0717 for REFA). FRAC1

and MOD1 are the 24-bit numerators and denominators of the

fractional feedback divider block. The fractional portion of the

feedback divider can be bypassed by setting FRAC1 to 0, but

MOD1 should never be 0.

The DPLL output frequency is usually 175 MHz to 200 MHz for

optimal performance.

TDC/PFD

The phase-frequency detector (PFD) is an all-digital block. It

compares the digital output from the TDC (which relates to the

active reference edge) with the digital word from the feedback

block. It uses a digital code pump and digital integrator (rather

than a conventional charge pump and capacitor) to generate the

error signal that steers the DCO frequency toward phase lock.

相关PDF资料 |

PDF描述 |

|---|---|

| V375C36M150BG | CONVERTER MOD DC/DC 36V 150W |

| AD9547BCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| D38999/20MF11JN | CONN RCPT 11POS WALL MNT W/SCKT |

| AD9549ABCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| ADN2814ACPZ | IC CLOCK/DATA RECOVERY 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9557BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 40LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9558 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Input Multiservice Line Card Adaptive |

| AD9558/PCBZ | 功能描述:BOARD EVAL FOR AD9558 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9558BCPZ | 功能描述:IC CLOCK TRANSLATOR 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9558BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。