参数资料

| 型号: | AD9557BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/92页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK TRANSLATOR 40LFCSP |

| 产品变化通告: | Minor Mask Change 11/Apr/2012 |

| 标准包装: | 1 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

Data Sheet

AD9557

Rev. B | Page 35 of 92

OUTPUT PLL (APLL)

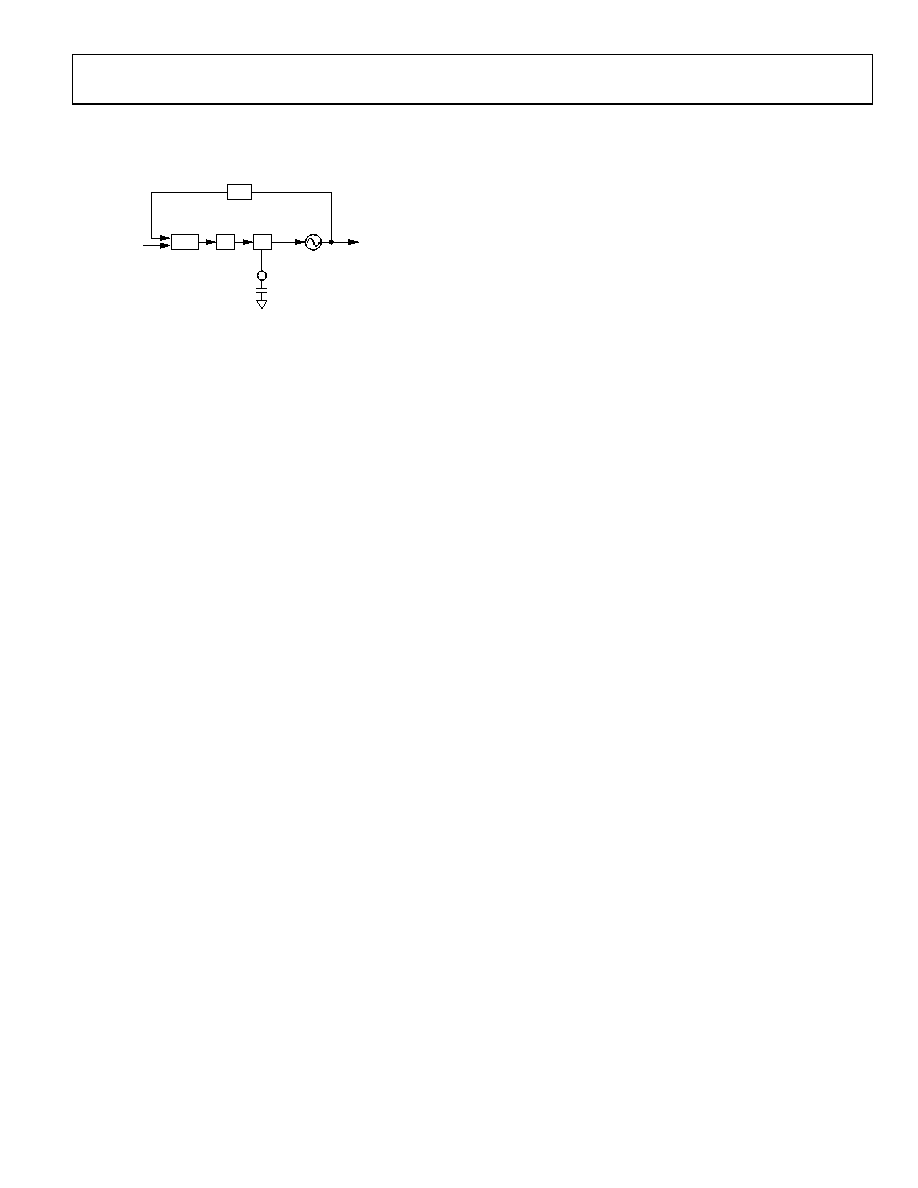

A diagram of the output PLL (APLL) is shown in Figure 39.

LF CAP

VCO2

3.35GHz TO 4.05GHz

PFD

FROM DPLL

TO CLOCK

DISTRIBUTION

LF

CP

INTEGER DIVIDER

OUTPUT PLL DIVIDER (APLL)

÷N2

09197-

138

Figure 39. Output PLL Block Diagram

The APLL provides the frequency upconversion from the DPLL

output to the 3.35 GHz to 4.05 GHz range, while also providing

noise filtering on the DPLL output. The APLL reference input is

the output of the DPLL. The feedback divider is an integer divider.

The loop filter is partially integrated with the one external 6.8 nF

capacitor. The nominal loop bandwidth for this PLL is 250 kHz,

with 68 degrees of phase margin.

The frequency wizard that is included in the evaluation software

configures the APLL, and the user should not need to make

changes to the APLL settings. However, there may be special cases

where the user may wish to adjust the APLL loop bandwidth to

meet a specific phase noise requirement. The easiest way to change

the APLL loop BW is to adjust the APLL charge pump current

in Register 0x0400. There is sufficient stability (68 of phase

margin) in the APLL default settings to permit a broad range of

adjustment without causing the APLL to be unstable. The user

should contact Analog Devices directly if more detail is needed.

Calibration of the APLL must be performed at startup and

whenever the nominal input frequency to the APLL changes by

more than ±100 ppm, although the APLL maintains lock over

voltage and temperature extremes without recalibration.

Calibration centers the dc operating voltage at the input to the

APLL VCO.

APLL calibration at startup can be accomplished during initial

register loading by following the instructions in the Device

this datasheet.

To recalibrate the APLL VCO after the chip has been running,

the user should first input the new settings (if any). Ensure that

the system clock is still locked and stable, and that the DPLL is

in free run mode with the free run tuning word set to the same

output frequency that is used when the DPLL is locked.

Use the following steps to calibrate the APLL VCO:

1. Ensure that the system clock is locked and stable.

2. Ensure that the DPLL is in user free run mode

(Register 0x0A01[5] = 1b), and the free run tuning word is set.

3. Write Register 0x0405 = 0x20.

4. Write Register 0x0005 = 0x01.

5. Write Register 0x0405 = 0x21.

6. Write Register 0x0005 = 0x01.

7. Monitor the APLL status using Bit 2 in Register 0x0D01.

相关PDF资料 |

PDF描述 |

|---|---|

| V375C36M150BG | CONVERTER MOD DC/DC 36V 150W |

| AD9547BCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| D38999/20MF11JN | CONN RCPT 11POS WALL MNT W/SCKT |

| AD9549ABCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| ADN2814ACPZ | IC CLOCK/DATA RECOVERY 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9557BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 40LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9558 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Input Multiservice Line Card Adaptive |

| AD9558/PCBZ | 功能描述:BOARD EVAL FOR AD9558 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9558BCPZ | 功能描述:IC CLOCK TRANSLATOR 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9558BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。