参数资料

| 型号: | AD9557BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/92页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK TRANSLATOR 40LFCSP |

| 产品变化通告: | Minor Mask Change 11/Apr/2012 |

| 标准包装: | 1 |

| 类型: | 时钟/频率转换器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,HSTL,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.25GHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

AD9557

Data Sheet

Rev. B | Page 48 of 92

I2C SERIAL PORT OPERATION

The I2C interface has the advantage of requiring only two control

pins and is a de facto standard throughout the I2C industry.

However, its disadvantage is programming speed, which is

400 kbps maximum. The AD9557 I2C port design is based on

the I2C fast mode standard; therefore, it supports both the 100 kHz

standard mode and 400 kHz fast mode. Fast mode imposes a glitch

tolerance requirement on the control signals. That is, the input

receivers ignore pulses of less than 50 ns duration.

The AD9557 I2C port consists of a serial data line (SDA) and

a serial clock line (SCL). In an I2C bus system, the AD9557 is

connected to the serial bus (data bus SDA and clock bus SCL)

as a slave device; that is, no clock is generated by the AD9557.

The AD9557 uses direct 16-bit memory addressing instead of

traditional 8-bit memory addressing.

The AD9557 allows up to seven unique slave devices to occupy

the I2C bus. These are accessed via a 7-bit slave address that is

transmitted as part of an I2C packet. Only the device that has a

matching slave address responds to subsequent I2C commands.

Table 24 lists the supported device slave addresses.

I2C Bus Characteristics

Table 29. I2C Bus Abbreviation Definitions

Abbreviation

Definition

S

Start

Sr

Repeated start

P

Stop

A

Acknowledge

A

E

Nonacknowledge

A

WE

Write

R

Read

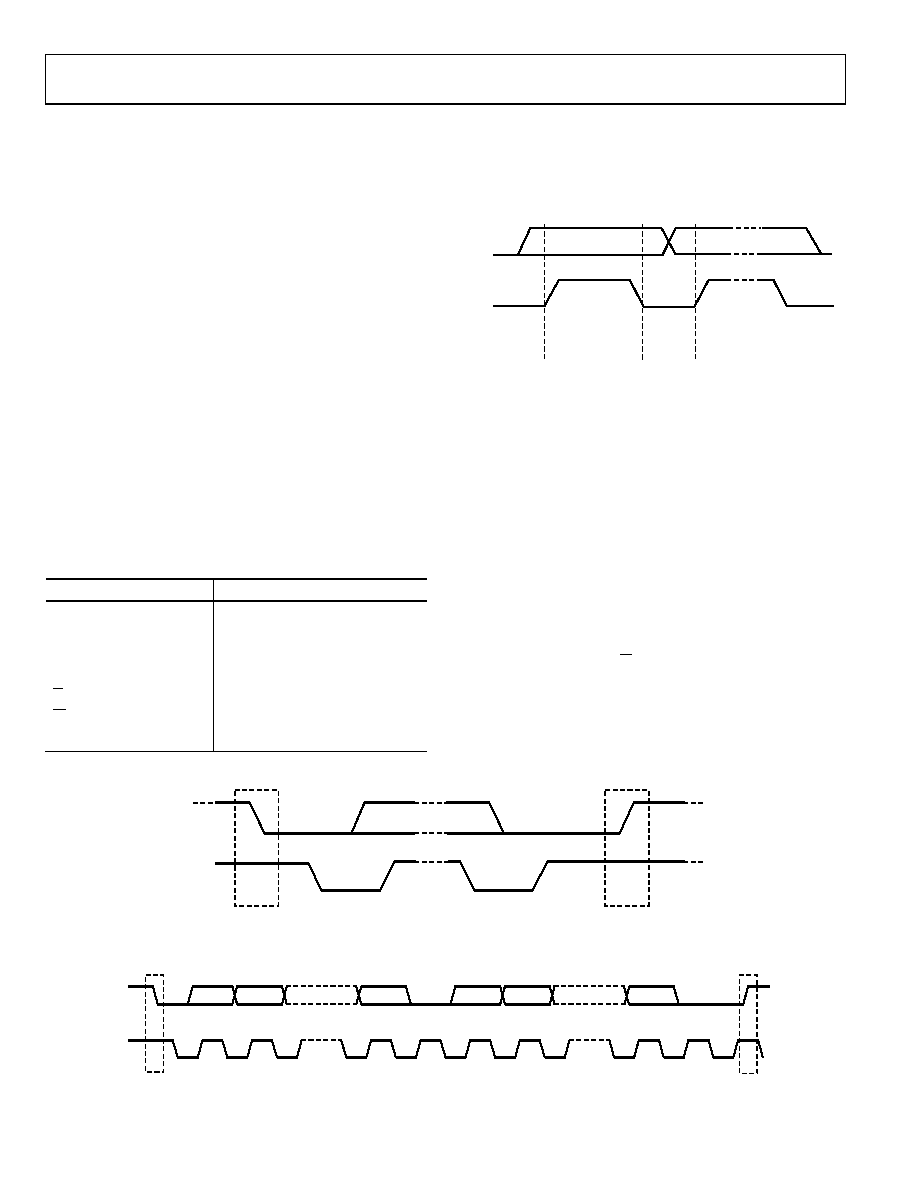

The transfer of data is shown in Figure 49. One clock pulse is

generated for each data bit transferred. The data on the SDA

line must be stable during the high period of the clock. The

high or low state of the data line can change only when the

clock signal on the SCL line is low.

DATA LINE

STABLE;

DATA VALID

CHANGE

OF DATA

ALLOWED

SDA

SCL

0

91

97-

035

Figure 49. Valid Bit Transfer

Start/stop functionality is shown in Figure 50. The start condition

is characterized by a high-to-low transition on the SDA line while

SCL is high. The start condition is always generated by the master

to initialize a data transfer. The stop condition is characterized

by a low-to-high transition on the SDA line while SCL is high.

The stop condition is always generated by the master to terminate

a data transfer. Every byte on the SDA line must be eight bits long.

Each byte must be followed by an acknowledge bit; bytes are sent

MSB first.

The acknowledge bit (A) is the ninth bit attached to any 8-bit

data byte. An acknowledge bit is always generated by the

receiving device (receiver) to inform the transmitter that the

byte has been received. It is done by pulling the SDA line low

during the ninth clock pulse after each 8-bit data byte.

The nonacknowledge bit (

A

AE

A

) is the ninth bit attached to any 8-

bit data byte. A nonacknowledge bit is always generated by the

receiving device (receiver) to inform the transmitter that the

byte has not been received. It is done by leaving the SDA line

high during the ninth clock pulse after each 8-bit data byte.

SDA

START CONDITION

STOP CONDITION

SCL

S

P

09

197-

036

Figure 50. Start and Stop Conditions

12

89

12

3TO 7

89

10

SDA

SCL

S

MSB

ACK FROM

SLAVE RECEIVER

ACK FROM

SLAVE RECEIVER

P

09197-

037

Figure 51. Acknowledge Bit

相关PDF资料 |

PDF描述 |

|---|---|

| V375C36M150BG | CONVERTER MOD DC/DC 36V 150W |

| AD9547BCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| D38999/20MF11JN | CONN RCPT 11POS WALL MNT W/SCKT |

| AD9549ABCPZ | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| ADN2814ACPZ | IC CLOCK/DATA RECOVERY 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9557BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 40LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9558 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Input Multiservice Line Card Adaptive |

| AD9558/PCBZ | 功能描述:BOARD EVAL FOR AD9558 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9558BCPZ | 功能描述:IC CLOCK TRANSLATOR 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9558BCPZ-REEL7 | 功能描述:IC CLK XLATR PLL 1250MHZ 64LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。