- 您现在的位置:买卖IC网 > PDF目录17028 > DK-DEV-3CLS200N (Altera)KIT DEV CYCLONE III LS EP3CLS200 PDF资料下载

参数资料

| 型号: | DK-DEV-3CLS200N |

| 厂商: | Altera |

| 文件页数: | 12/34页 |

| 文件大小: | 0K |

| 描述: | KIT DEV CYCLONE III LS EP3CLS200 |

| 产品培训模块: | Cyclone® III FPGA Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 1 |

| 系列: | Cyclone® III |

| 类型: | FPGA |

| 适用于相关产品: | EP3CLS200 |

| 所含物品: | 板 |

| 产品目录页面: | 606 (CN2011-ZH PDF) |

| 相关产品: | 544-2564-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2563-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2562-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2561-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2560-ND - IC CYCLONE III FPGA 5K 256 UBGA 544-2559-ND - IC CYCLONE III FPGA 5K 164 MBGA 544-2558-ND - IC CYCLONE III FPGA 5K 256 FBGA 544-2557-ND - IC CYCLONE III FPGA 5K 144 EQFP 544-2556-ND - IC CYCLONE III FPGA 55K 484 UBGA 544-2554-ND - IC CYCLONE III FPGA 55K 780 FBGA 更多... |

| 其它名称: | 544-2601 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

�

�1–12�

�Chapter� 1:� Cyclone� III� Device� Datasheet�

�Electrical� Characteristics�

�f� For� more� illustrations� of� receiver� input� and� transmitter� output� waveforms,� and� for�

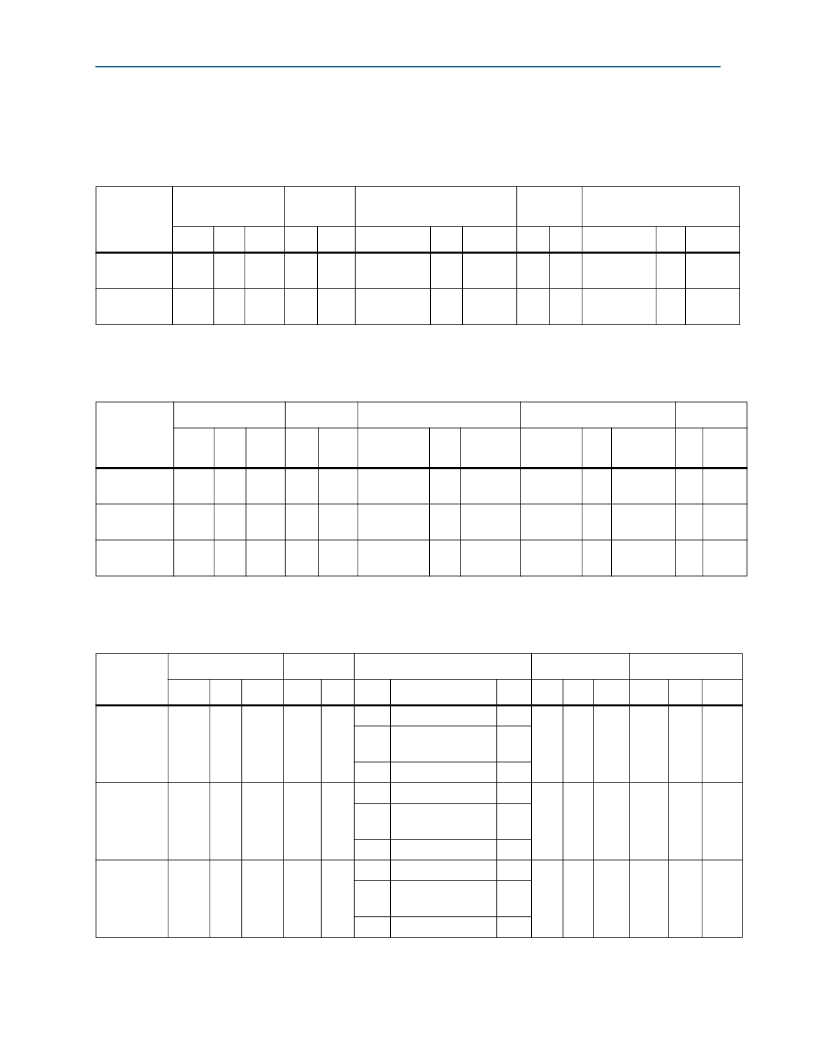

���Table� 1–16.� Cyclone� III� Devices� Differential� SSTL� I/O� Standard� Specifications� (1)�

�I/O� Standard�

�V� CCIO� (V)�

�V� Swing(DC)� (V)�

�V� X(AC)� (V)�

�V� Swing(AC)�

�(V)�

�V� OX(AC)� (V)�

�Min�

�Typ�

�Max�

�Min�

�Max�

�Min�

�Typ�

�Max�

�Min� Max�

�Min�

�Typ�

�Max�

�SSTL-2�

�Class� I,� II�

�2.375�

�2.5�

�2.625� 0.36� V� CCIO� V� CCIO� /2� –� 0.2�

�—�

�V� CCIO� /2�

�+� 0.2�

�0.7�

�V� CCI�

�O�

�V� CCIO� /2� –�

�0.125�

�—�

�V� CCIO� /2�

�+� 0.125�

�SSTL-18�

�Class� I,� II�

�1.7�

�1.8�

�1.90�

�0.25� V� CCIO�

�V� CCIO� /2� –�

�0.175�

�—�

�V� CCIO� /2�

�+� 0.175�

�0.5�

�V� CCI�

�O�

�V� CCIO� /2� –�

�0.125�

�—�

�V� CCIO� /2�

�+� 0.125�

��(1)� Differential� SSTL� requires� a� V� REF� input.�

�Table� 1–17.� Cyclone� III� Devices� Differential� HSTL� I/O� Standard� Specifications� (1)�

�V� CCIO� (V)�

�V� DIF(DC)� (V)�

�V� X(AC)� (V)�

�V� CM(DC)� (V)�

�V� DIF(AC)� (V)�

�I/O� Standard�

�HSTL-18�

�Class� I,� II�

�HSTL-15�

�Class� I,� II�

�HSTL-12�

�Class� I,� II�

�Min�

�1.71�

�1.425�

�1.14�

�Typ�

�1.8�

�1.5�

�1.2�

�Max�

�1.89�

�1.575�

�1.26�

�Min�

�0.2�

�0.2�

�0.16�

�Max�

�—�

�—�

�V� CCIO�

�Min�

�0.85�

�0.71�

�0.48� *� V� CCIO�

�Typ�

�—�

�—�

�—�

�Max�

�0.95�

�0.79�

�0.52� *�

�V� CCIO�

�Min�

�0.85�

�0.71�

�0.48� *�

�V� CCIO�

�Typ�

�—�

�—�

�—�

�Max�

�0.95�

�0.79�

�0.52� *�

�V� CCIO�

�Mi�

�n�

�0.4�

�0.4�

�0.3�

�Max�

�—�

�—�

�0.48� *�

�V� CCIO�

��(1)� Differential� HSTL� requires� a� V� REF� input.�

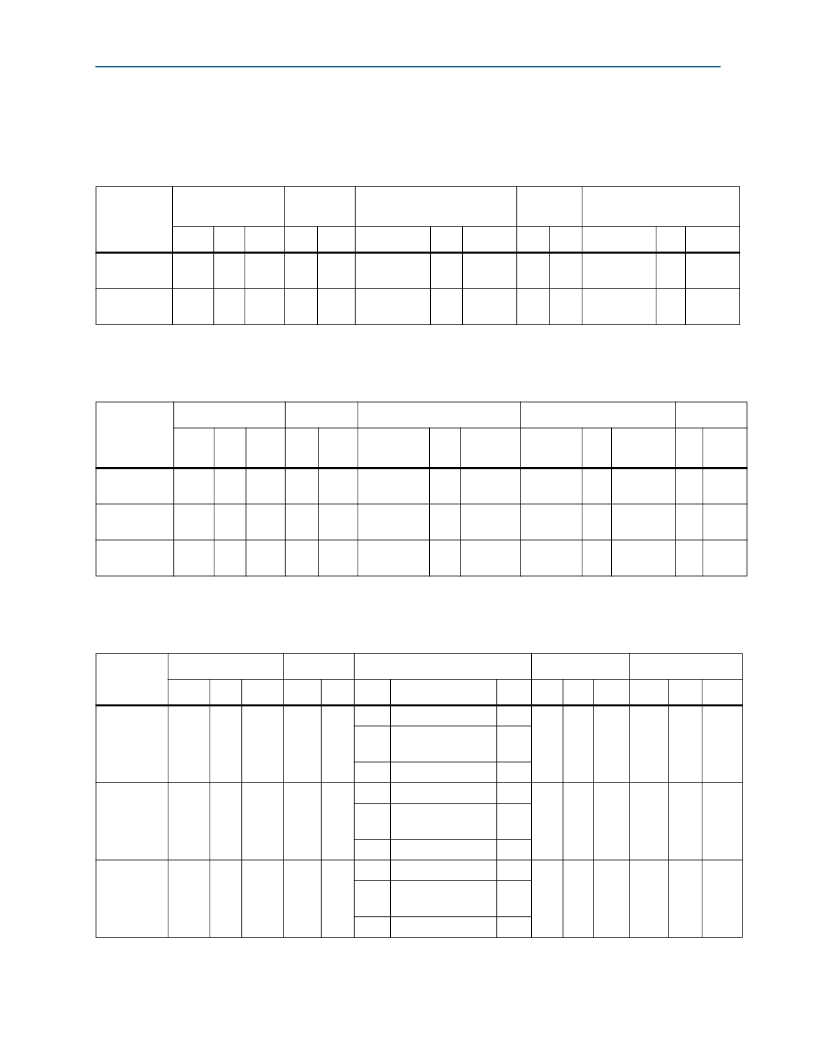

�Table� 1–18.� Cyclone� III� Devices� Differential� I/O� Standard� Specifications�

�(1)�

�(Part� 1� of� 2)�

�I/O�

�V� CCIO� (V)�

�V� ID� (mV)�

�V� IcM� (V)�

�(2)�

�V� OD� (mV)�

�(3)�

�V� OS� (V)�

�(3)�

�Standard�

�Min�

�Typ�

�Max�

�Min�

�Max�

�Min�

�Condition�

�Max� Min� Typ�

�Max�

�Min�

�Typ�

�Max�

�500� Mbps� ?� D� MAX�

�?� 700� Mbps�

�LVPECL�

�(Row� I/Os)�

�(4)�

�2.375�

�2.5�

�2.625�

�100�

�—�

�0.05� D� MAX� ???� 500� Mbps�

�0.55�

�1.80�

�1.80�

�—�

�—�

�—�

�—�

�—�

�—�

�1.05� D� MAX� >� 700� Mbps�

�1.55�

�500� Mbps� ?� D� MAX�

�??� 700� Mbps�

�LVPECL�

�(Column�

�I/Os)� (4)�

�2.375�

�2.5�

�2.625�

�100�

�—�

�0.05� D� MAX� ??� 500� Mbps�

�0.55�

�1.80�

�1.80�

�—�

�—�

�—�

�—�

�—�

�—�

�1.05� D� MAX� >� 700� Mbps�

�0.05� D� MAX� ??� 500� Mbps�

�1.55�

�1.80�

�LVDS� (Row�

�I/Os)�

�2.375�

�2.5�

�2.625�

�100�

�—�

�0.55�

�500� Mbps� ?� D� MAX�

�?� 700� Mbps�

�1.80� 247�

�—�

�600�

�1.125� 1.25� 1.375�

���1.05� D� MAX� >� 700� Mbps�

�1.55�

�July� 2012� Altera� Corporation�

�相关PDF资料 |

PDF描述 |

|---|---|

| FPF2000 | IC SW LOAD FULL FUNC 50MA SC70-5 |

| DC1813A-A | BOARD SAR ADC LTC2370-16 |

| EEM25DRYF | CONN EDGECARD 50POS DIP .156 SLD |

| VE-B5V-EY | CONVERTER MOD DC/DC 5.8V 50W |

| ESM10DREN | CONN EDGECARD 20POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-3SL150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F152 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N/ES | 制造商:Altera Corporation 功能描述:KIT DEVELOPMENT STRATIX II ES |

| DK-DEV-4CGX150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4CGX150 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4CGX150N | 制造商:Altera Corporation 功能描述:KIT STARTER CYCLONE IV GX ((NS |

| DK-DEV-4S100G5N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4S100G5F RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。