- 您现在的位置:买卖IC网 > PDF目录17028 > DK-DEV-3CLS200N (Altera)KIT DEV CYCLONE III LS EP3CLS200 PDF资料下载

参数资料

| 型号: | DK-DEV-3CLS200N |

| 厂商: | Altera |

| 文件页数: | 9/34页 |

| 文件大小: | 0K |

| 描述: | KIT DEV CYCLONE III LS EP3CLS200 |

| 产品培训模块: | Cyclone® III FPGA Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 1 |

| 系列: | Cyclone® III |

| 类型: | FPGA |

| 适用于相关产品: | EP3CLS200 |

| 所含物品: | 板 |

| 产品目录页面: | 606 (CN2011-ZH PDF) |

| 相关产品: | 544-2564-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2563-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2562-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2561-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2560-ND - IC CYCLONE III FPGA 5K 256 UBGA 544-2559-ND - IC CYCLONE III FPGA 5K 164 MBGA 544-2558-ND - IC CYCLONE III FPGA 5K 256 FBGA 544-2557-ND - IC CYCLONE III FPGA 5K 144 EQFP 544-2556-ND - IC CYCLONE III FPGA 55K 484 UBGA 544-2554-ND - IC CYCLONE III FPGA 55K 780 FBGA 更多... |

| 其它名称: | 544-2601 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

�

�Chapter� 1:� Cyclone� III� Device� Datasheet�

�Electrical� Characteristics�

�Internal� Weak� Pull-Up� and� Weak� Pull-Down� Resistor�

��devices.�

�1–9�

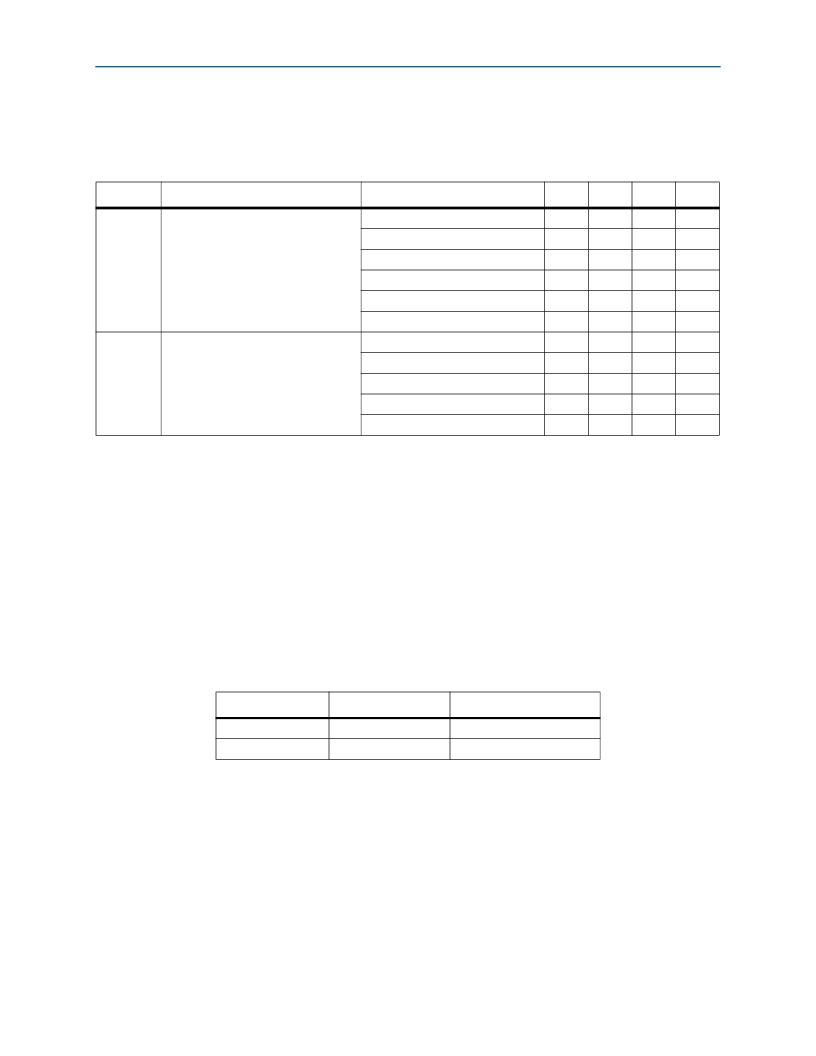

�Table� 1–10.� Cyclone� III� Devices� Internal� Weak� Pull-Up� and� Weak� Pull-Down� Resistor�

�(1)�

�Symbol�

�Parameter�

�Conditions�

��V� CCIO� =� 3.3� V� ±� 5%�

�Min�

�7�

�Typ�

�25�

�Max�

�41�

�Unit�

�k� ?�

�R� _PU�

�R� _PD�

�Value� of� I/O� pin� pull-up� resistor� before�

�and� during� configuration,� as� well� as�

�user� mode� if� the� programmable�

�pull-up� resistor� option� is� enabled�

�Value� of� I/O� pin� pull-down� resistor�

�before� and� during� configuration�

�V� CCIO� =� 3.0� V� ±� 5%�

�V� CCIO� =� 2.5� V� ±� 5%�

�V� CCIO� =� 1.8� V� ±� 5%�

�V� CCIO� =� 1.5� V� ±� 5%�

�V� CCIO� =� 1.2� V� ±� 5%�

�V� CCIO� =� 3.3� V� ±� 5%�

�V� CCIO� =� 3.0� V� ±� 5%�

�V� CCIO� =� 2.5� V� ±� 5%�

�V� CCIO� =� 1.8� V� ±� 5%�

�V� CCIO� =� 1.5� V� ±� 5%�

������(4)�

�(4)�

�(4)�

�(4)�

�(4)�

�7�

�8�

�10�

�13�

�19�

�6�

�6�

�6�

�7�

�8�

�28�

�35�

�57�

�82�

�143�

�19�

�22�

�25�

�35�

�50�

�47�

�61�

�108�

�163�

�351�

�30�

�36�

�43�

�71�

�112�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

�k� ?�

��(1)� All� I/O� pins� have� an� option� to� enable� weak� pull-up� except� configuration,� test,� and� JTAG� pin.� Weak� pull-down� feature� is� only� available� for� JTAG�

�TCK.�

�(2)� Pin� pull-up� resistance� values� may� be� lower� if� an� external� source� drives� the� pin� higher� than� V� CCIO� .�

�(3)� R� _PU� =� (V� CCIO� –� V� I� )/I� R_PU�

�Minimum� condition:� –40°C;� V� CCIO� =� V� CC� +� 5%,� V� I� =� V� CC� +� 5%� –� 50� mV;�

�Typical� condition:� 25°C;� V� CCIO� =� V� CC� ,� V� I� =� 0� V;�

�Maximum� condition:� 125°C;� V� CCIO� =� V� CC� –� 5%,� V� I� =� 0� V;� in� which� V� I� refers� to� the� input� voltage� at� the� I/O� pin.�

�(4)� R� _PD� =� V� I� /I� R_PD�

�Minimum� condition:� –40°C;� V� CCIO� =� V� CC� +� 5%,� V� I� =� 50� mV;�

�Typical� condition:� 25°C;� V� CCIO� =� V� CC� ,� V� I� =� V� CC� –� 5%;�

�Maximum� condition:� 125°C;� V� CCIO� =� V� CC� –� 5%,� V� I� =� V� CC� –� 5%;� in� which� V� I� refers� to� the� input� voltage� at� the� I/O� pin.�

�Hot� Socketing�

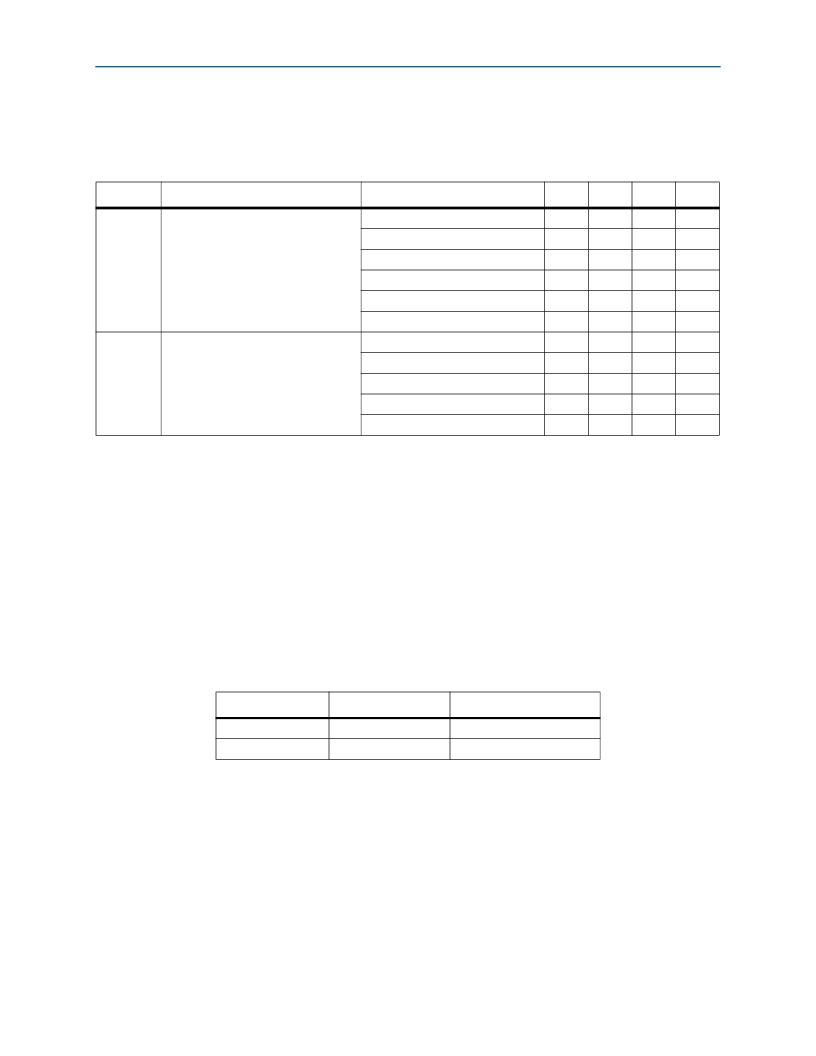

��Table� 1–11.� Cyclone� III� Devices� Hot-Socketing� Specifications�

�Symbol�

�I� IOPIN(DC)�

�Parameter�

�DC� current� per� I/O� pin�

�Maximum�

�300� ?� A�

�I� IOPIN(AC)�

�AC� current� per� I/O� pin�

�8� mA�

�(1)�

��(1)� The� I/O� ramp� rate� is� 10� ns� or� more.� For� ramp� rates� faster� than� 10� ns,� |IIOPIN|� =� C�

�dv/dt,� in� which� C� is� I/O� pin� capacitance� and� dv/dt� is� the� slew� rate.�

�July� 2012�

�Altera� Corporation�

���相关PDF资料 |

PDF描述 |

|---|---|

| FPF2000 | IC SW LOAD FULL FUNC 50MA SC70-5 |

| DC1813A-A | BOARD SAR ADC LTC2370-16 |

| EEM25DRYF | CONN EDGECARD 50POS DIP .156 SLD |

| VE-B5V-EY | CONVERTER MOD DC/DC 5.8V 50W |

| ESM10DREN | CONN EDGECARD 20POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-3SL150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F152 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N/ES | 制造商:Altera Corporation 功能描述:KIT DEVELOPMENT STRATIX II ES |

| DK-DEV-4CGX150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4CGX150 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4CGX150N | 制造商:Altera Corporation 功能描述:KIT STARTER CYCLONE IV GX ((NS |

| DK-DEV-4S100G5N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4S100G5F RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。