- 您现在的位置:买卖IC网 > PDF目录17028 > DK-DEV-3CLS200N (Altera)KIT DEV CYCLONE III LS EP3CLS200 PDF资料下载

参数资料

| 型号: | DK-DEV-3CLS200N |

| 厂商: | Altera |

| 文件页数: | 5/34页 |

| 文件大小: | 0K |

| 描述: | KIT DEV CYCLONE III LS EP3CLS200 |

| 产品培训模块: | Cyclone® III FPGA Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 1 |

| 系列: | Cyclone® III |

| 类型: | FPGA |

| 适用于相关产品: | EP3CLS200 |

| 所含物品: | 板 |

| 产品目录页面: | 606 (CN2011-ZH PDF) |

| 相关产品: | 544-2564-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2563-ND - IC CYCLONE III FPGA 80K 484 UBGA 544-2562-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2561-ND - IC CYCLONE III FPGA 80K 484 FBGA 544-2560-ND - IC CYCLONE III FPGA 5K 256 UBGA 544-2559-ND - IC CYCLONE III FPGA 5K 164 MBGA 544-2558-ND - IC CYCLONE III FPGA 5K 256 FBGA 544-2557-ND - IC CYCLONE III FPGA 5K 144 EQFP 544-2556-ND - IC CYCLONE III FPGA 55K 484 UBGA 544-2554-ND - IC CYCLONE III FPGA 55K 780 FBGA 更多... |

| 其它名称: | 544-2601 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

�

�Chapter� 1:� Cyclone� III� Device� Datasheet�

�1–5�

�Electrical� Characteristics�

�DC� Characteristics�

�This� section� lists� the� I/O� leakage� current,� pin� capacitance,� on-chip� termination� (OCT)�

�tolerance,� and� bus� hold� specifications� for� Cyclone� III� devices.�

�Supply� Current�

�Standby� current� is� the� current� the� device� draws� after� the� device� is� configured� with� no�

�inputs� or� outputs� toggling� and� no� activity� in� the� device.� Use� the� Excel-based� early�

�power� estimator� (EPE)� to� get� the� supply� current� estimates� for� your� design� because�

�these� currents� vary� largely� with� the� resources� used.� Table� 1–4� lists� I/O� pin� leakage�

�current� for� Cyclone� III� devices.�

�f� For� more� information� about� power� estimation� tools,� refer� to� the� PowerPlay� Early� Power�

��Handbook� .�

��(2)�

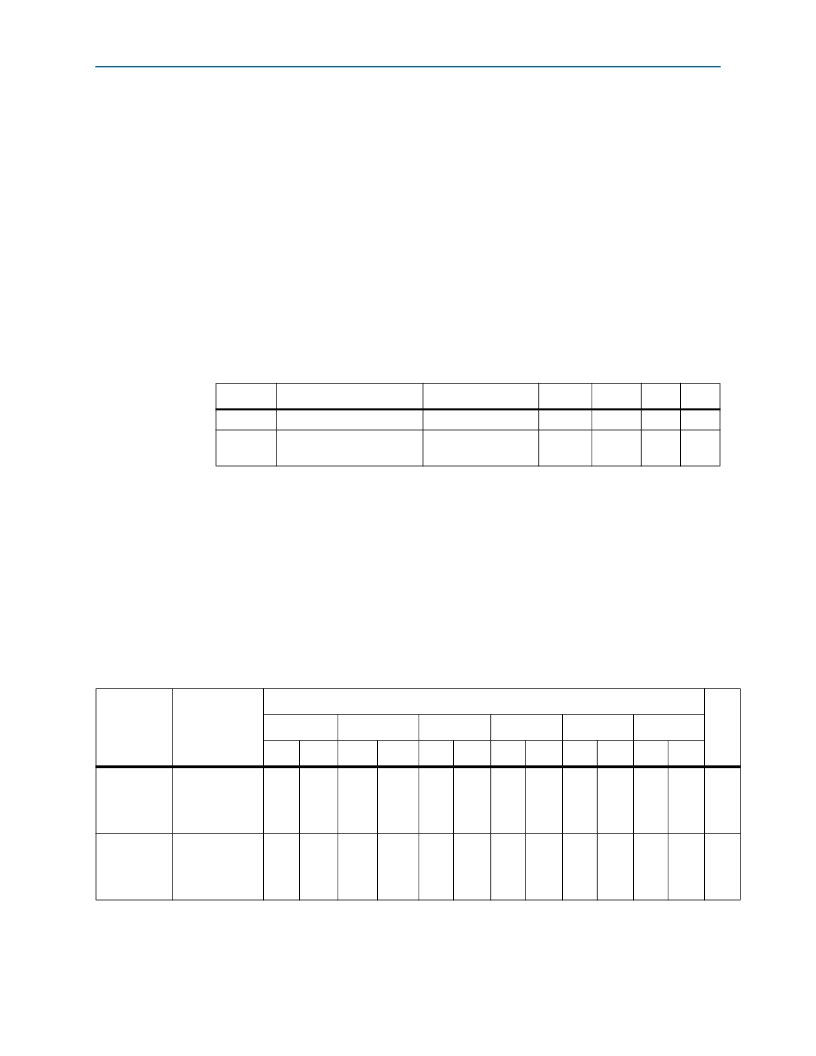

�Symbol�

�I� I�

�I� OZ�

�Parameter�

�Input� pin� leakage� current�

�Tristated� I/O� pin� leakage�

�current�

�Conditions�

�V� I� =� 0� V� to� V� CCIOMAX�

�V� O� =� 0� V� to� V� CCIOMAX�

�Min�

�–10�

�–10�

�Typ�

�—�

�—�

�Max�

�10�

�10�

�Unit�

�?� A�

�?� A�

��(1)� This� value� is� specified� for� normal� device� operation.� The� value� varies� during� device� power-up.� This� applies� for� all�

�V� CCIO� settings� (3.3,� 3.0,� 2.5,� 1.8,� 1.5,� and� 1.2� V).�

�(2)� 10� ?� A� I/O� leakage� current� limit� is� applicable� when� the� internal� clamping� diode� is� off.� A� higher� current� can� be� the�

�observed� when� the� diode� is� on.�

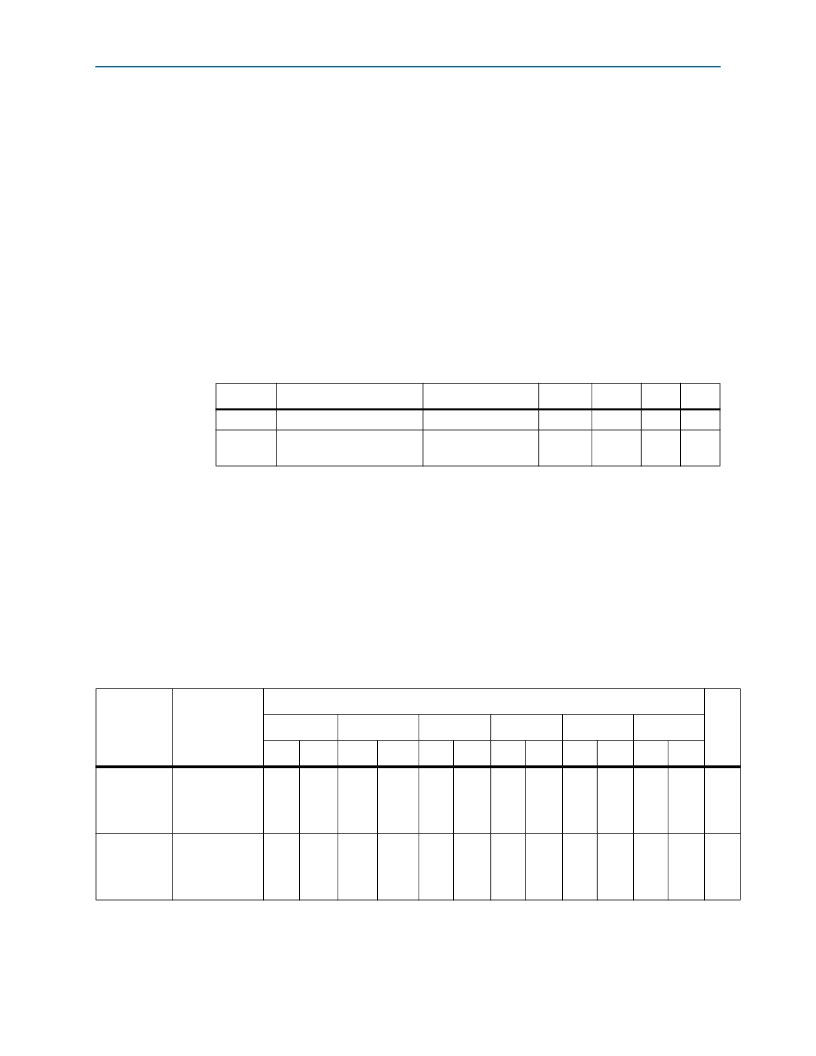

�Bus� Hold�

�Bus� hold� retains� the� last� valid� logic� state� after� the� source� driving� it� either� enters� the�

�high� impedance� state� or� is� removed.� Each� I/O� pin� has� an� option� to� enable� bus� hold� in�

�user� mode.� Bus� hold� is� always� disabled� in� configuration� mode.�

��Table� 1–5.� Cyclone� III� Devices� Bus� Hold� Parameter�

�(Part� 1� of� 2)�

�(1)�

�V� CCIO� (V)�

�Parameter�

�Condition�

�1.2�

�1.5�

�1.8�

�2.5�

�3.0�

�3.3�

�Unit�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�Bus-hold�

�low,�

�sustaining�

�V� IN� >� V� IL�

�(maximum)�

�8�

�—�

�12�

�—�

�30�

�—�

�50�

�—�

�70�

�—�

�70�

�—�

�?� A�

�current�

�Bus-hold�

�high,�

�sustaining�

�V� IN� <� V� IL�

�(minimum)�

�–8�

�—�

�–12�

�—�

�–30�

�—�

�–50�

�—�

�–70�

�—�

�–70�

�—�

�?� A�

�current�

�July� 2012�

�Altera� Corporation�

���相关PDF资料 |

PDF描述 |

|---|---|

| FPF2000 | IC SW LOAD FULL FUNC 50MA SC70-5 |

| DC1813A-A | BOARD SAR ADC LTC2370-16 |

| EEM25DRYF | CONN EDGECARD 50POS DIP .156 SLD |

| VE-B5V-EY | CONVERTER MOD DC/DC 5.8V 50W |

| ESM10DREN | CONN EDGECARD 20POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-3SL150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F152 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N/ES | 制造商:Altera Corporation 功能描述:KIT DEVELOPMENT STRATIX II ES |

| DK-DEV-4CGX150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4CGX150 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-4CGX150N | 制造商:Altera Corporation 功能描述:KIT STARTER CYCLONE IV GX ((NS |

| DK-DEV-4S100G5N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4S100G5F RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。