- 您现在的位置:买卖IC网 > PDF目录67681 > IBM21P100BGB PCI BUS CONTROLLER, PBGA304 PDF资料下载

参数资料

| 型号: | IBM21P100BGB |

| 元件分类: | 总线控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封装: | 31 X 31 MM, HEAT SINK, PLASTIC, BGA-304 |

| 文件页数: | 102/140页 |

| 文件大小: | 2032K |

| 代理商: | IBM21P100BGB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页当前第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页

IBM21P100BGB

IBM 133 PCI-X Bridge R1.1

Configuration Registers

Page 56 of 131

ppb11_pcix_regs.fm.03

July 9, 2001

5.2.5 Device-Specific Configuration Space Registers

The following sections are register by register descriptions of the Device-Specific Configuration Space

Region.

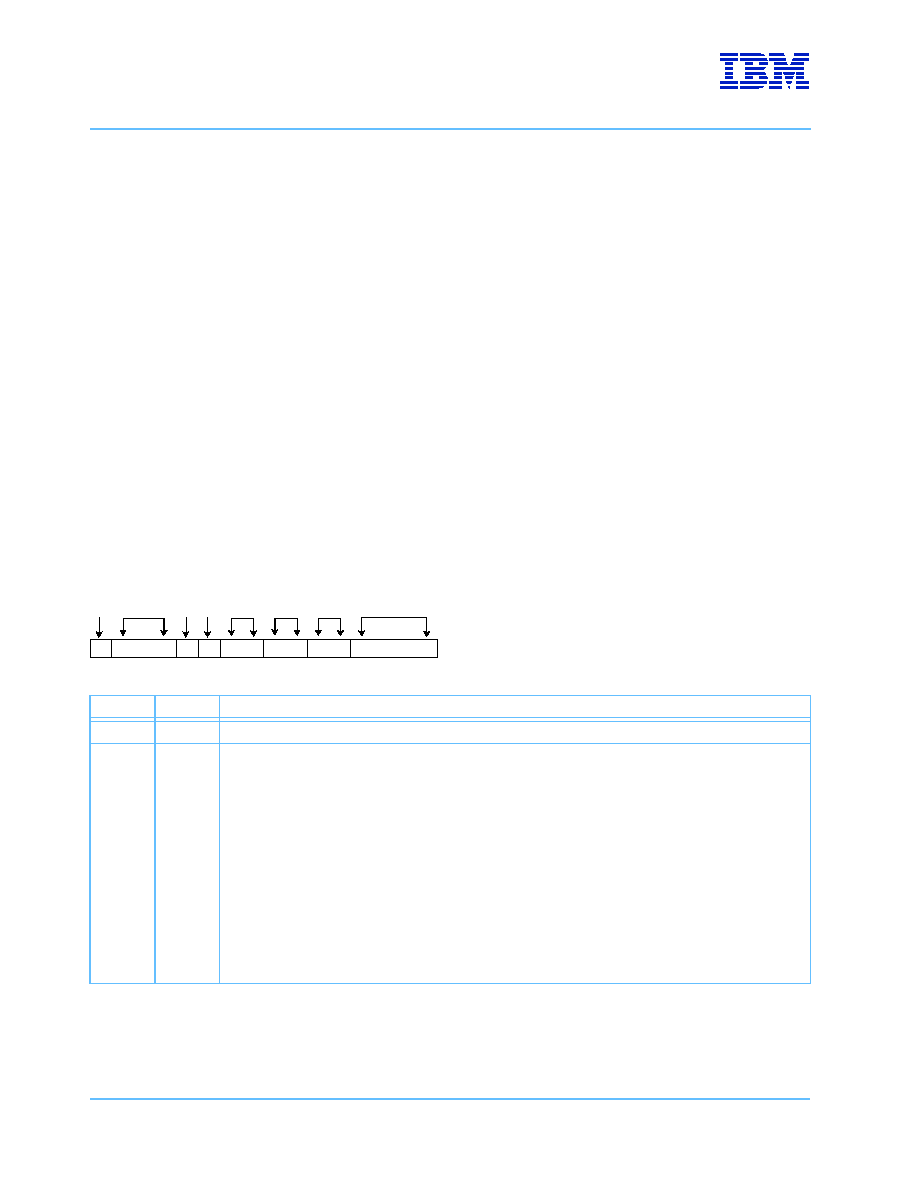

5.2.5.1 Primary Data Buffering Control Register

The Primary Data Buffering Control register provides controls for memory read transactions that are initiated

on the primary interface.

Address Offset

x‘40’

Access

See individual bit fields.

Reset Value

x‘0020’

Res

e

rv

ed

M

a

ximum

M

emor

y

R

e

a

d

B

yt

e

C

ount

E

n

a

b

le

Relax

e

d

O

rdering

Pr

im

ary

S

p

e

cial

Delayed

R

ead

Mode

Pr

im

ary

R

ead

Pref

et

ch

bit

s

Pr

im

ary

R

ead

Line

P

ref

et

ch

bit

s

Pr

im

ary

R

ead

Mult

ip

le

Pre

fet

ch

bi

ts

Reserved

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Bit(s)

Access

Field Name and Description

15

RO

Reserved

14:12

RW

Maximum Memory Read Byte Count

These bits set the maximum byte count used by the bridge when generating read requests on the secondary

bus in response to a memory read operation initiated on the primary bus (when the primary bus is in PCI

mode). Device drivers must not modify these bits without considering the impact on the rest of the system.

These bits only have an effect if the prefetch mode bits for the PCI read command in use (bits (9:8), (7:6), or

(5:4) below) are set to “full prefetch”. The most recent value of this register is used each time the bridge makes

a new read request. The bits have the following meaning:

000

default to 512 bytes

001

128 bytes

010

256 bytes

011

512 bytes

100

1024 bytes

101

2048 bytes

110

4096 bytes

111

default to 512 bytes

相关PDF资料 |

PDF描述 |

|---|---|

| IBM21P100BGC | PCI BUS CONTROLLER, PBGA304 |

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

发布紧急采购,3分钟左右您将得到回复。