- 您现在的位置:买卖IC网 > PDF目录67685 > ICS1890Y-14 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ICS1890Y-14 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | TQFP-64 |

| 文件页数: | 12/66页 |

| 文件大小: | 1749K |

| 代理商: | ICS1890Y-14 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

2

ICS1890

Introduction

The ICS1890 is essentially a nibble/bit stream processor.

When transmitting, it takes sequential nibbles presented at

the Media Independent Interface (MII) and translates them to

aserial bitstream for transmissionon themedia. When receiving,

it takes the serial bit stream from the media and translates it to

sequential nibbles for presentation to the MII. It has no

knowledge of the underlying structure of the MAC frame it is

conveying.

100Base-TX Operation

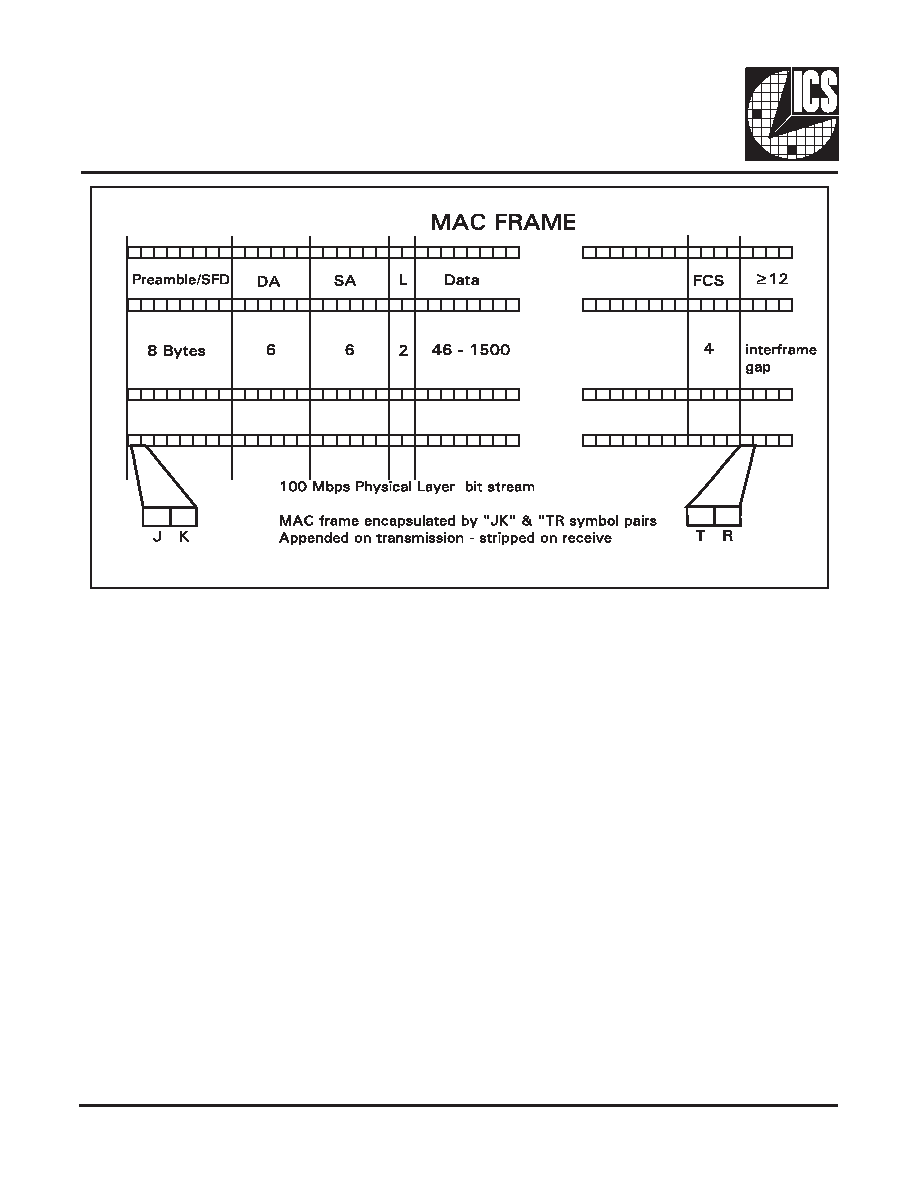

When transmitting, the ICS1890 encapsulates the MAC

frame (including the preamble) with the start-of-stream and

end-of-stream delimiters. When receiving, it strips off the

SSD and substitutes the normal preamble pattern and then

presents this and subsequent preamble nibbles to the MII.

When it encounters the ESD, it ends the presentation of

nibbles to the MII. Thus, the MAC reconciliation layer sees

an exact copy of the transmitted frame.

During periods when no frames are being transmitted or

received, the device signals and detects the idle condition.

This allows the higher levels to determine the integrity of the

connection. In the 100Base-TX mode, a continuous stream of

scrambled ones is transmitted signifying the idle condition.

The receive channel includes logic that monitors the IDLE

data stream to look for this pattern and thereby establishes

the link integrity.

The 100M Stream Interface option allows access to raw groups

of 5-bit data with lower latency through the PHY. This is useful

in building repeaters where latency is critical.

10Base-T Operation

In 10Base-T mode, the bit stream on the cable is identical to

the de-composed MAC frame. Link pulses are used to establish

the channel integrity. When receiving, the ICS1890 first

synchronizes to the preamble. Once lock is detected, it begins

to present preamble nibbles to the MII. On detection of the

SFD, it frames the subsequent 4-bits which are the first data

nibble.

Configuration

The ICS1890 is designed to be fully configurable using

either hardware pins or the (usually) software-driven MII

Management interface, as selected with the HW/SW pin. A

rich set of configuration options are provided. This allows

diverse system implementations and costs.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS2059GI-02 | 27 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS2304NZGI-1T | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS2304NZG-1LF | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS252MI-XXLF | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS252MI-XX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1890Y-4 | 制造商:ICS 功能描述:1890Y-4 |

| ICS1891 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1891Y | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1892 | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

发布紧急采购,3分钟左右您将得到回复。