- 您现在的位置:买卖IC网 > PDF目录67685 > ICS1890Y-14 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ICS1890Y-14 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | TQFP-64 |

| 文件页数: | 65/66页 |

| 文件大小: | 1749K |

| 代理商: | ICS1890Y-14 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页当前第65页第66页

8

ICS1890

Functional Blocks

Media Independent Interface (MII) Overview

The MII consists of a data interface, basic register set, and a

serial management interface to the register set.

The data interface is a nibble wide transmit and receive data

interface between the MAC and PHY devices. The interface

supports data transfers at 25 MHz for 100Base-T and 2.5 MHz

for 10Base-T.

The register set consists of basic and extended standard

registers as well as vendor specific registers. There are two

basic registers, a control register to handle basic device

configuration, and a status register to report basic device

abilities and status. The standard extended registers provide

access to an Organizationally Unique Identifier and Auto-

Negotiation functionality.

The ICS1890 also provides vendor specific registers that

enhance the device operation. Among these is the QuickPoll

Detailed Status register which provides a comprehensive set

of real-time device information with only single register access.

Auto-Negotiation

The auto-negotiation logic of the ICS1890 has three main

purposes. Firstly, to determine the capabilities of the remote

partner (device at the other end of the cable). Secondly, to

advertise its own capabilities to the remote partner.And thirdly,

to establish a connection with the remote partner using the

highest performance common connection technology.

The ICS1890 auto-negotiation logic is designed to operate

with legacy 10Base-T networks or newer systems with multiple

connection technology options. When operating with a legacy

10Base-T remote partner, theICS1890will select the 10Base-

T operating mode transparently to the remote partner thus

allowing the preservation of existing legacy network structures

without management intervention.

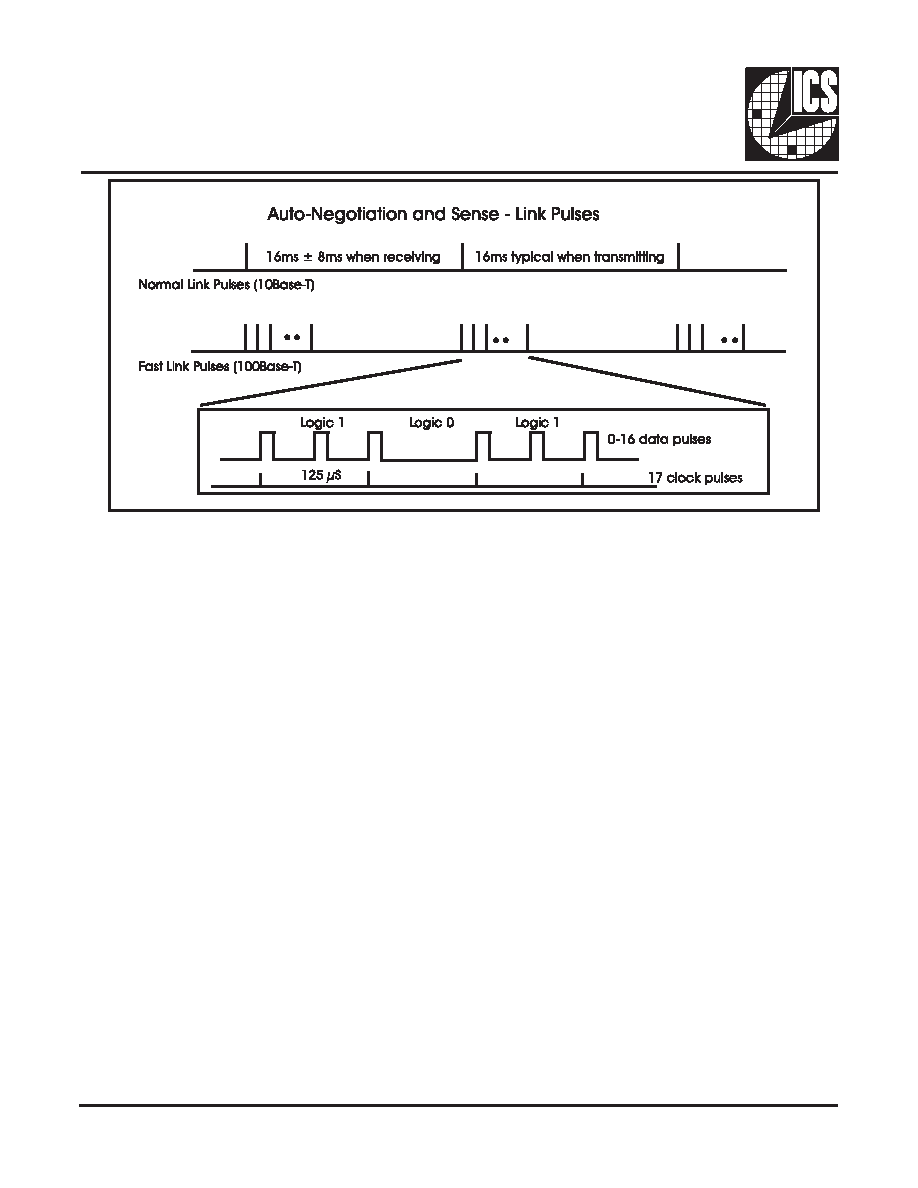

Auto-negotiation is accomplished using a physical signaling

scheme that is transparent at the packet and higher level

protocols. This scheme builds upon the 10Base-T link test

pulse sequence by using a burst of pulses to signal

configuration information between the two devices.

The Fast Link Pulse Bursts are simultaneously exchanged by

both nodes on a link segment the local node encodes the data

from the Auto-negotiation Advertisement Register (register

4) into the FLP Bursts it transmits. The data received from the

link partners FLP Bursts is placed into the Auto-Negotiation

LinkPartnerAbilityRegister(register5).WhenAuto-Negotiation

is complete (1:5=1 or 17:4=1), the highest priority technology

from the following table that is common in the two registers is

automatically selected as the operating mode.

Priority ResolutionTable

Highest Priority Listed first.

1)

100Base-TXFullDuplex

2)

100Base-T4

3)

100Base-TX

4)

10Base-T Full Duplex

5)

10Base-T

相关PDF资料 |

PDF描述 |

|---|---|

| ICS2059GI-02 | 27 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS2304NZGI-1T | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS2304NZG-1LF | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS252MI-XXLF | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS252MI-XX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1890Y-4 | 制造商:ICS 功能描述:1890Y-4 |

| ICS1891 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1891Y | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1892 | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

发布紧急采购,3分钟左右您将得到回复。