- 您现在的位置:买卖IC网 > PDF目录67685 > ICS1890Y-14 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ICS1890Y-14 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 100M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 封装: | TQFP-64 |

| 文件页数: | 39/66页 |

| 文件大小: | 1749K |

| 代理商: | ICS1890Y-14 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

44

ICS1890

When configuration through Auto-Negotiation is selected,

the DPXSEL and 10/100SEL settings control the Auto-

Negotiation register 4 default settings and Auto-Negotiation

is enabled. When configuration without Auto-Negotiation is

selected DPXSEL controls the duplex setting and 10/100SEL

controls the data rate setting.

When this pin is a logic one, software bits have priority over

hardware pin settings. The 10/100SEL pin becomes an output

indicating the link speed when the link is established and

parallels bit (17:15). The DPXSEL pin becomes an output

indicating the link duplex state when the link is established

and parallels bit (17:14). The ANSEL pin becomes an output

indicating whether auto-negotiation is being used and parallels

bit(0:12).

10/100 Select

10/100SEL

This pin is an input or an output depending on the setting of

the HW/SW pin.

In HW mode, it is an input and controls speed selection

directly or through Auto-Negotiation. When the input is low,

10Base-T is selected. When the input is high, 100Base-TX is

selected.

In SW mode, this pin is an output and correctly reflects the

selected speed when the link is established (LSTAis asserted).

The output is low when 10Base-T is selected and high when

100Base-TX is selected which gives the same indication as

register bit (17:15).

Note this pin also affects the MAC - PHY interface that is used

in conjunction with the MII/SI pin.

Duplex Select

DPXSEL

This pin is an input or an output depending on the setting of

the HW/SW pin.

In HW mode, it is an input and controls duplex selection

directly or through Auto-Negotiation. When the input is low,

Half Duplex is selected. When the input is high, Full Duplex is

selected.

In SW mode, this pin is an output and correctly reflects the

selected duplex mode when the link is established (LSTA is

asserted). The output is low when Half Duplex is selected and

highwhenFullDuplexisselectedwhichgivesthesameindication

as register bit (17:14).

In Full Duplex mode, CRS is asserted only on receive activity.

In Full Duplex mode, COLis disabled and always remains low.

Auto-Negotiation Select

ANSEL

This pin is an input or output depending on the setting of the

HW/SW pin.

In HW mode, it is an input and controls the enabling of Auto-

Negotiation.When the input is low,Auto-Negotiationisdisabled.

When the input is high, Auto-Negotiation is enabled and the

single technology selected by 10/100SEL and DPXSEL is

advertised.

In SW mode, this pin is an output and reflects whether Auto-

Negotiation has been enabled or disabled. The output is low

when Auto-Negotiation is disabled and high when Auto-

Negotiation is enabled which gives the same indication as

register bit (0:12).

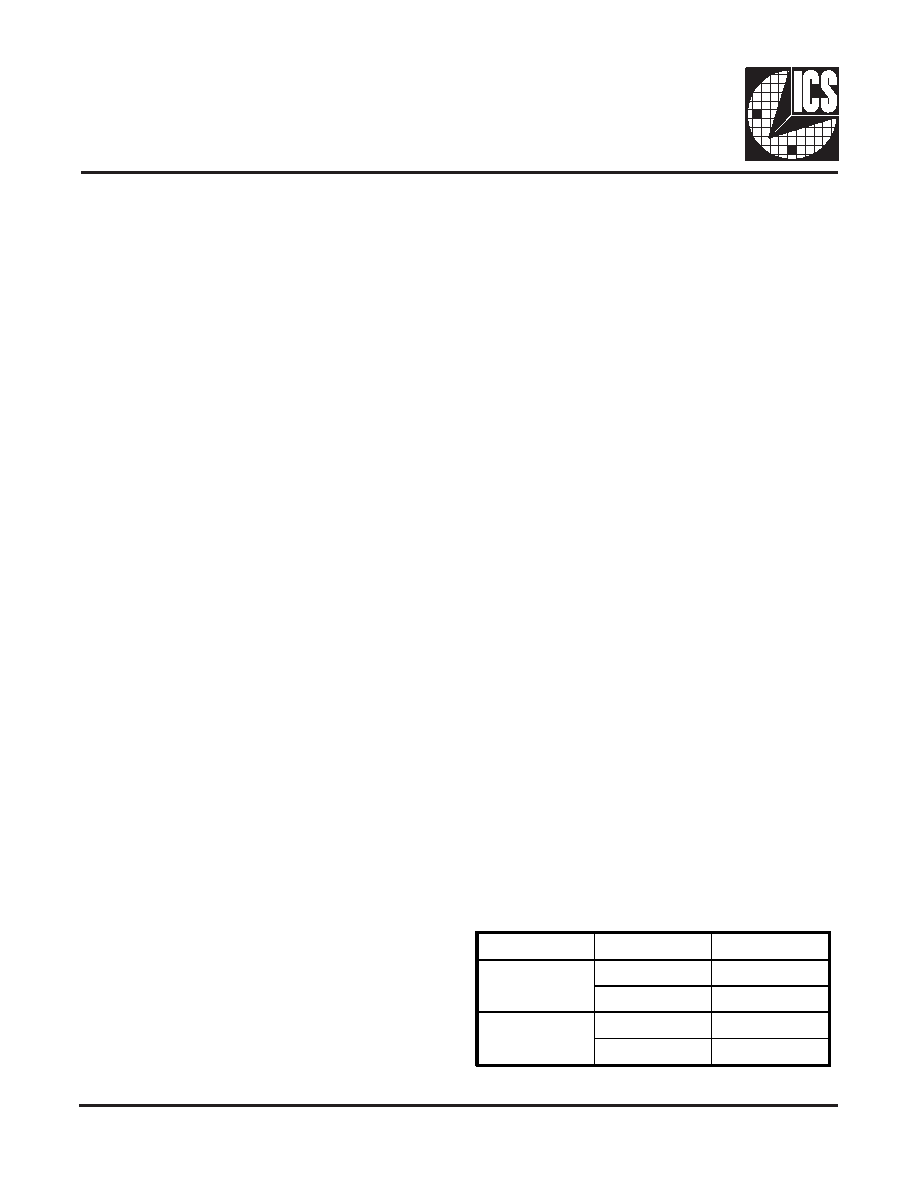

Invert Transmit Clock Latching Setting ITCLS~

The ICS1890 allows transmit data to be latched relative to

either TXCLK or REF_IN. Latching the data to TXCLK is the

behavior specified in the 100Base-T MII specification, but in

some applications it is desirable to latch data with the REF_IN

clock. An example of where this might be beneficial is in a

repeater application where all data transmission on multiple

1890s need to be synchronized to a common clock.

To select the proper setting of this pin, first choose the setting

of the NOD/REP pin. Then select the setting of the ITCLS pin

that latches the transmit data with the clock of your choice.

The following table shows the possible combinations. This

pin has an internal pull-up so it may be left not connected for

some applications.

Hardware/Software Priority Select

HW/SW

When this pin is logic zero, hardware pins have priority over

software settings. The 10/100SEL pin becomes an input and

controls speed selection. The DPXSEL pin becomes an input

and controls duplex selection. The ANSEL pin becomes an

inputandchoosesconfigurationwithorwithoutAuto-Negotiation.

NOD/REP

ITCLS

Latching Clock

NOD

(0)

0

REF_IN

1

TXCLK

REP

(1)

0

TXCLK

1

REF_IN

相关PDF资料 |

PDF描述 |

|---|---|

| ICS2059GI-02 | 27 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| ICS2304NZGI-1T | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS2304NZG-1LF | 2304 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS252MI-XXLF | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS252MI-XX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1890Y-4 | 制造商:ICS 功能描述:1890Y-4 |

| ICS1891 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1891Y | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| ICS1892 | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y | 制造商:ICS 制造商全称:ICS 功能描述:10Base-T/100Base-TX Integrated PHYceiver |

发布紧急采购,3分钟左右您将得到回复。