- 您现在的位置:买卖IC网 > PDF目录229297 > MT46V32M8BG-6AT:G 32M X 8 DDR DRAM, 0.7 ns, PBGA60 PDF资料下载

参数资料

| 型号: | MT46V32M8BG-6AT:G |

| 元件分类: | DRAM |

| 英文描述: | 32M X 8 DDR DRAM, 0.7 ns, PBGA60 |

| 封装: | (8 X 14) MM, LEAD FREE,PLASTIC, FBGA-60 |

| 文件页数: | 86/93页 |

| 文件大小: | 3632K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页当前第86页第87页第88页第89页第90页第91页第92页第93页

PDF: 09005aef80768abb/Source: 09005aef82a95a3a

Micron Technology, Inc., reserves the right to change products or specifications without notice.

DDR_x4x8x16_Core2.fm - 256Mb DDR: Rev. O, Core DDR: Rev. B 1/09 EN

85

2003 Micron Technology, Inc. All rights reserved.

256Mb: x4, x8, x16 DDR SDRAM

Operations

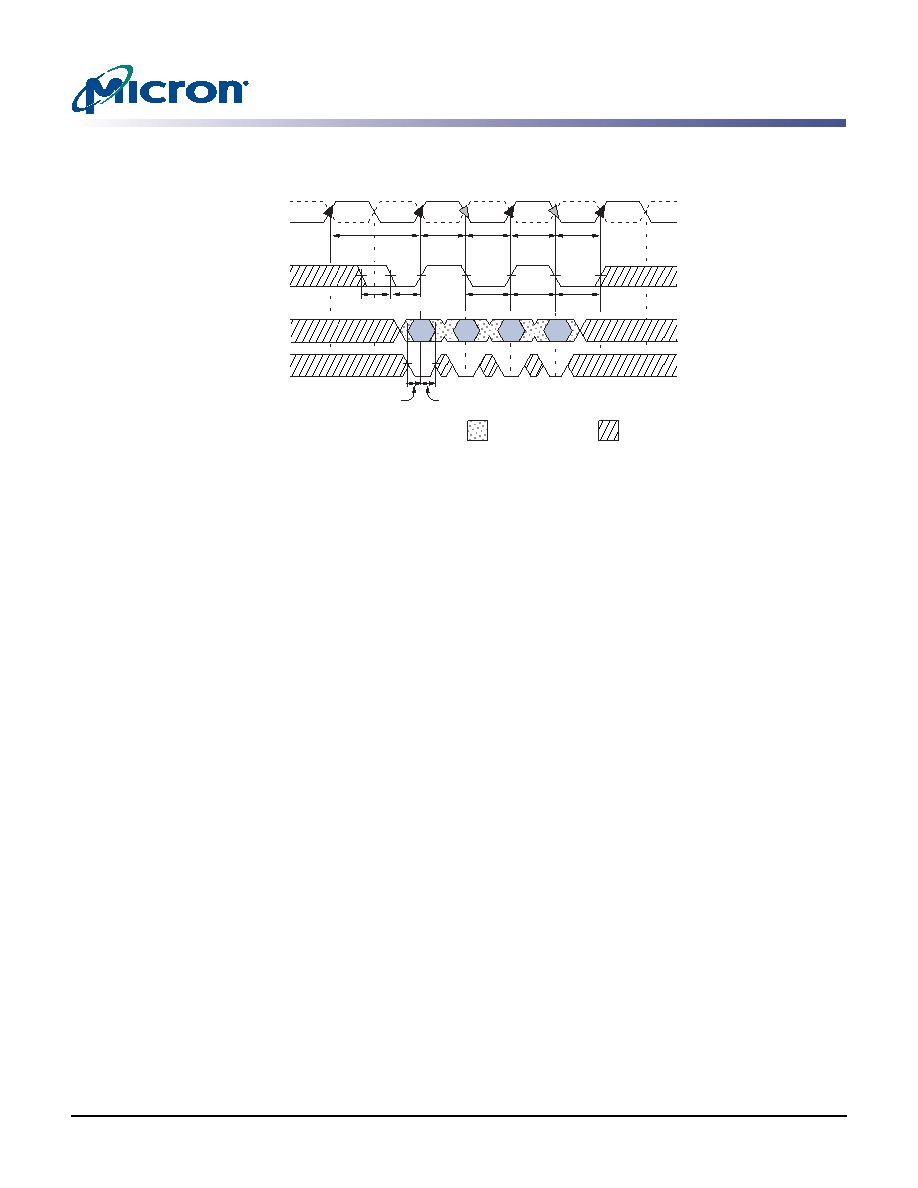

Figure 50:

Data Input Timing

Notes:

1. WRITE command issued at T0.

2. tDSH (MIN) generally occurs during tDQSS (MIN).

3. tDSS (MIN) generally occurs during tDQSS (MAX).

4. For x16, LDQS controls the lower byte and UDQS controls the upper byte.

5. DI b = data-in from column b.

PRECHARGE

The bank(s) will be available for a subsequent row access a specified time (tRP) after the

PRECHARGE command is issued, except in the case of concurrent auto precharge. With

concurrent auto precharge, a READ or WRITE command to a different bank is allowed as

long as it does not interrupt the data transfer in the current bank and does not violate

any other timing parameters. Input A10 determines whether one or all banks are to be

precharged, and in the case where only one bank is to be precharged, inputs BA0, BA1

select the bank. When all banks are to be precharged, BA0, BA1 are treated as “Don’t

Care.” Once a bank has been precharged, it is in the idle state and must be activated

prior to any READ or WRITE commands being issued to that bank. A PRECHARGE

command will be treated as a NOP if there is no open row in that bank (idle state), or if

the previously open row is already in the process of precharging.

Auto Precharge

Auto precharge is a feature which performs the same individual-bank precharge func-

tion described above, but without requiring an explicit command. This is accomplished

by using A10 to enable auto precharge in conjunction with a specific READ or WRITE

command. A precharge of the bank/row that is addressed with the READ or WRITE

command is automatically performed upon completion of the READ or WRITE burst.

Auto precharge is either enabled or disabled for each individual READ or WRITE

command. This device supports concurrent auto precharge if the command to the other

bank does not interrupt the data transfer to the current bank.

Auto precharge ensures that the precharge is initiated at the earliest valid stage within a

burst. This “earliest valid stage” is determined as if an explicit PRECHARGE command

was issued at the earliest possible time, without violating tRAS (MIN), as described for

each burst type in “Operations” on page 52. The user must not issue another command

to the same bank until the precharge time (tRP) is completed.

T0

1

tDSH2

tDSS3

DI

b

DQS

tDQSS

tDQSH tWPST

tDH

tDS

tDQSL

DM

DQ

CK

CK#

T1

T1n

T2

T2n

T3

Don’t Care

Transitioning Data

tWPRE

tWPRES

相关PDF资料 |

PDF描述 |

|---|---|

| M29F800FB55N3E2 | 512K X 16 FLASH 5V PROM, 55 ns, PDSO48 |

| MC12L1NZGF | ROTARY SWITCH-12POSITIONS, SP12T, LATCHED, 0.25A, 28VDC, PANEL MOUNT-THREADED |

| MD00S1NCQF | ROTARY SWITCH-6POSITIONS, DP6T, LATCHED, 0.25A, 28VDC, THROUGH HOLE-STRAIGHT |

| MD06L1NZGD | ROTARY SWITCH-6POSITIONS, DP6T, LATCHED, 0.25A, 28VDC, PANEL MOUNT-THREADED |

| MD06L2NCQD | ROTARY SWITCH-6POSITIONS, DP6T, LATCHED, 0.25A, 28VDC, THROUGH HOLE-STRAIGHT |

相关代理商/技术参数 |

参数描述 |

|---|

发布紧急采购,3分钟左右您将得到回复。