- 您现在的位置:买卖IC网 > PDF目录299581 > ORLI10G1BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | ORLI10G1BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 26/78页 |

| 文件大小: | 1689K |

| 代理商: | ORLI10G1BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页

Lattice Semiconductor

ORCA ORLI10G Data Sheet

32

XGMII ORCA 4E Receive Analysis

XGMII Considerations

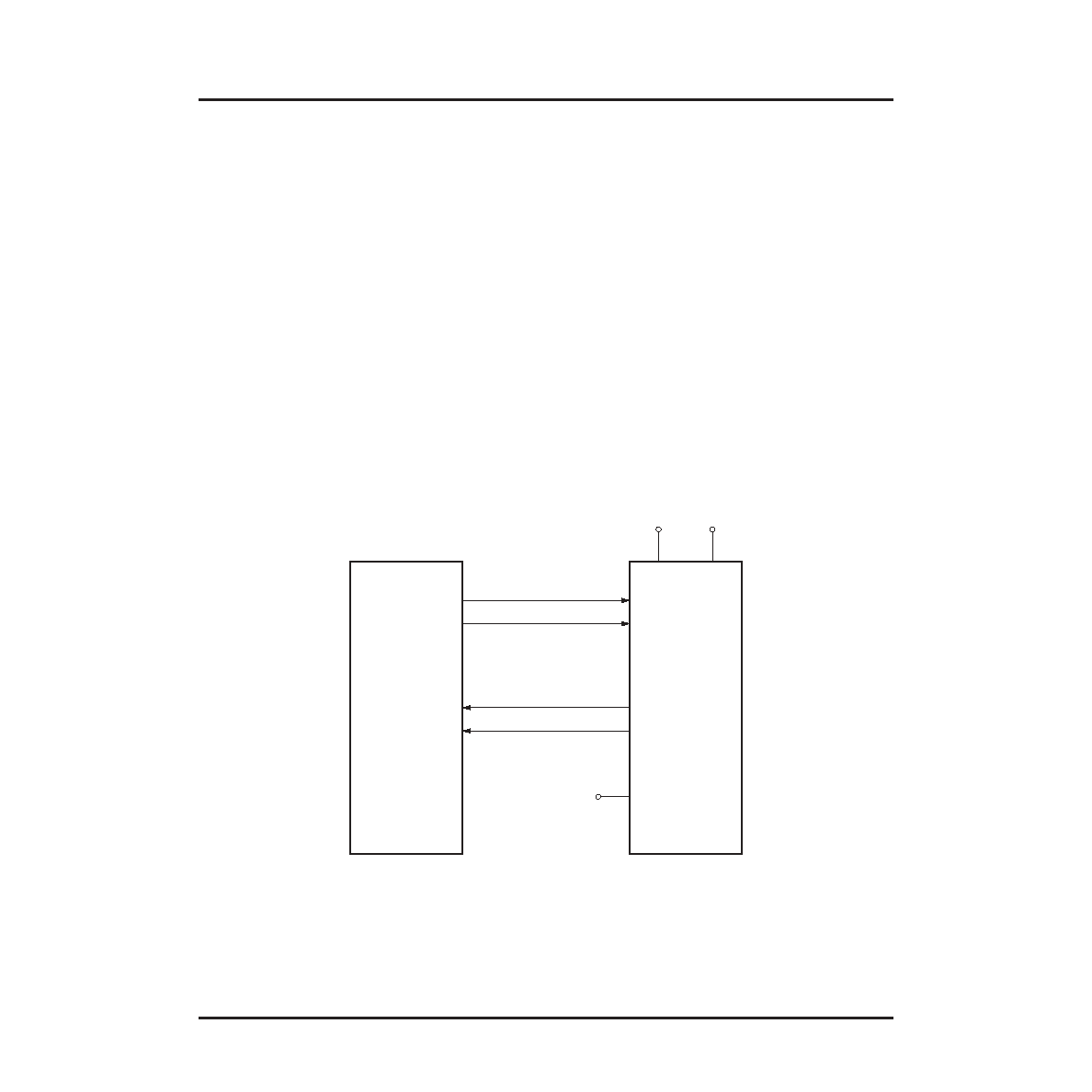

The stringent 10 Gbit Media Independent Interface (XGMII) specications from the IEEE 802.3ae standards are

met in the FPGA side of the ORLI10G device. This interface is implemented in the PCS IP core and targeted to the

ORLI10G FPSC. Figure 18 shows a simplied block diagram for the XGMII interface. Other I/O standards are also

possible, such as SSTL or HSTL, with a reference voltage of 1.8 V. Further details are available in the Series 4 I/O

application note and the Series 4 Fast Input DDR and Output DDR with Clock Forwarding Application Note.

The ORLI10G device meets the 480 ps input setup time and 480 ps input hold time requirements for the XGMII

receiver inputs into the FPGA side of the FPSC with the embedded I/O DDR cells on the FPGA side of the FPSC.

The PLLs are not used on input because this is a forward clocked interface. The ORLI10G meets the clock-to-out

specication on the XGMII DDR outputs by using the output shift register to produce a non-duty-cycle-dependent

output. An embedded output DDR capability is also available. The output clock is then centered around this data

eye using internal PLLs.

There are two considerations to note about the pinout location of the XGMII input clocks:

1.

The XGMII input clocks must be located at the C pad of the programmable I/O cells (PICs). In the pinout tables,

the pads are labeled on a pin-by-pin basis. For example, a pin whose pad is referenced as PL1C can be used

as an XGMII input clock, but pins referenced as PL1A, PL1B, or PL1D cannot be used as an XGMII input clock.

2.

The XGMII input data pins can be no further then six PICs away from the XGMII input clock pin.

Figure 18. Simplied XGMII Block Diagram

HSTL

CLOCK

VDDIO

VDD15

VDDIO = 1.5 V NOM

HSTL

VDDIO = 1.5 V NOM

VREF

VDDIO ÷ 2

DDR DATA

CUSTOMER DEVICE

ORLI10G

SYSTEM

INTERFACE

LINE

INTERFACE

相关PDF资料 |

PDF描述 |

|---|---|

| ORLI10G2BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| ORLI10G3BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| ORT82G5-1BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| ORT82G5-2BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| ORT82G5-3BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ORLI10G-1BM680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 316 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORLI10G-1BMN680C | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 316 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORLI10G-1BMN680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 316 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORLI10G-2BM680C | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 316 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| ORLI10G-2BM680I | 功能描述:FPGA - 现场可编程门阵列 10368 LUT 316 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。