- 您现在的位置:买卖IC网 > PDF目录11652 > AD9992BBCZ (Analog Devices Inc)IC CCD SGNL PROC 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9992BBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/92页 |

| 文件大小: | 0K |

| 描述: | IC CCD SGNL PROC 12BIT 105CSPBGA |

| 产品变化通告: | AD9992 Discontinuation 22/Feb/2012 |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,12 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 27mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

AD9992

Rev. C | Page 42 of 92

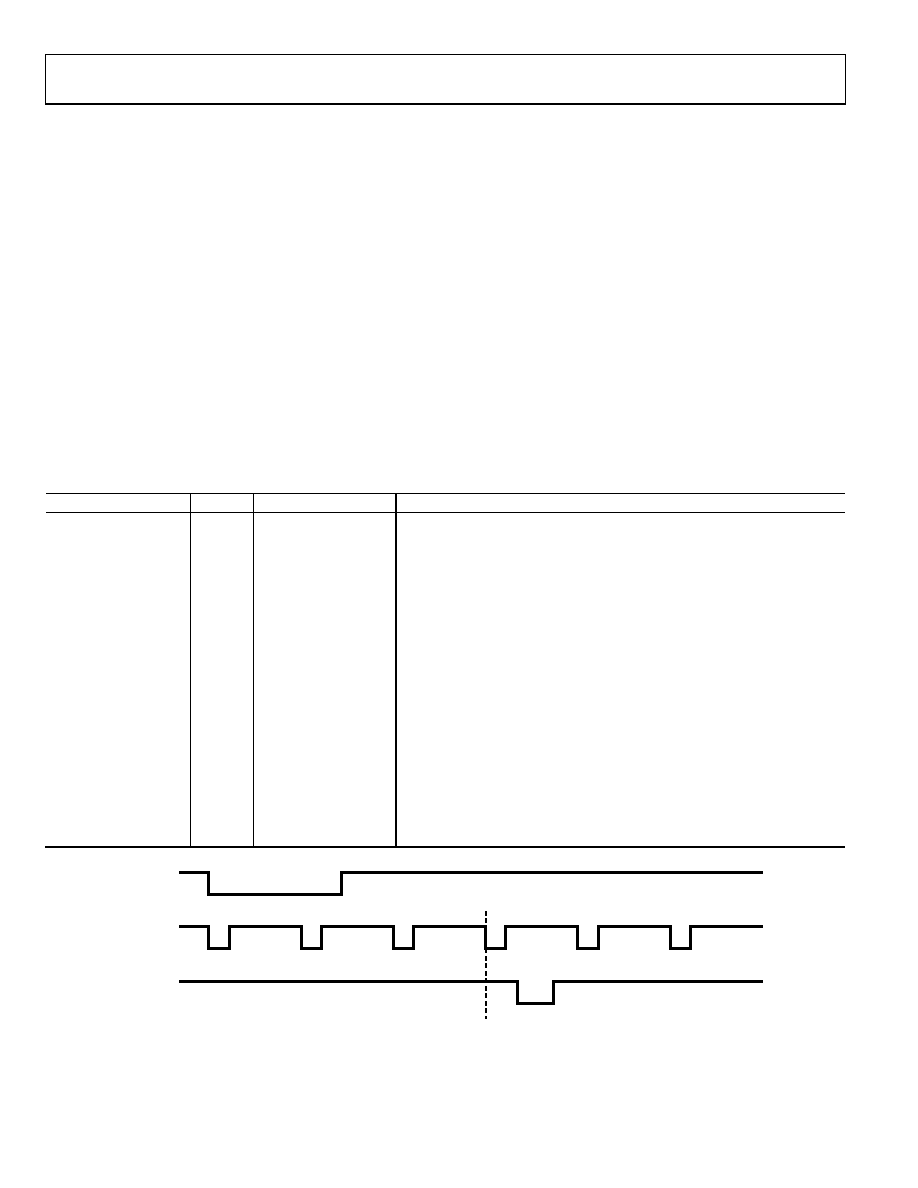

Vertical Sensor Gate (Shift Gate) Patterns

In an interline CCD, the vertical sensor gate (VSG) pulses are

used to transfer the pixel charges from the light-sensitive image

area into light-shielded vertical registers. From the light-

shielded vertical registers, the image is clocked out line-by-line

using the vertical transfer pulses (XV signals) in conjunction

with the high speed horizontal clocks. The AD9992 has 24

vertical signals, and each signal can be assigned as a VSG pulse

instead of an XV pulse.

Table 19 summarizes the VSG control registers, which are mostly

located in the field registers space (see Table 17). The VSGSELECT

register (Address 0x1C in the fixed address space) determines

which vertical outputs are assigned as VSG pulses. When a signal

is selected to be a VSG pulse, only the starting polarity and two of

the V-pattern toggle positions are used. The VSGPATSEL register

in the sequence registers is used to assign either XVTOG1 and

XVTOG2 or XVTOG3 and XVTOG4 to the VSG signal.

Note that only two of the four V-pattern toggle positions are

available when a vertical signal is selected to be a VSG pulse.

The SGACTLINE1 and SGACTLINE2 registers are used to

select which line in the field is the VSG line. The VSG active

line location is used to reference when the substrate clocking

(SUBCK) signal begins to operate in each field. For more

information, see the Substrate Clock Operation (SUBCK)

section.

Also located in the field registers, the SGMASK register selects

which individual VSG pulses are active in a given field. Therefore,

all SG patterns to be preprogrammed into the V-pattern registers

and the appropriate pulses for the different fields can be enabled

separately.

Table 19. VSG Control Registers (Also see Field Registers in Table 17)

Register

Length

Range

Description

24b

High/low

Selection of VSG signals from XV signals. Set to 1 to make signal a VSG.

[0]: XV1 selection (0 = XV pulse; 1 = VSG pulse).

VSGSELECT

(Located in Fixed

Address Space, 0x1C)

[1]: XV2 selection.

…

[23]: XV24 selection.

VSGPATSEL

24b

High/low

When VSG signal is selected using the VSGSELECT register, VSGPATSEL

selects which V-pattern toggle positions are used. When set to 0, Toggle 1

and Toggle 2 are used. When set to 1, Toggle 3 and Toggle 4 are used.

[0]: XV1 selection (0 = use XVTOG1, XVTOG2; 1 = use XVTOG3, XVTOG4).

[1]: XV2 selection.

…

[23]: XV24 selection.

SGMASK

24b

High/low, each VSG

Set high to mask each individual VSG output.

[0]: XV1 mask.

…

[23]: XV24 mask.

SGACTLINE1

13b

0 to 8191 line number

Selects the line in the field where the VSG signals are active.

SGACTLINE2

13b

0 to 8191 line number

Selects a second line in the field to repeat the VSG signals. If not used,

set this equal to SGACTLINE1 or to the maximum value.

VD

HD

VSG PATTERN

4

12

3

PROGRAMMABLE SETTINGS FOR EACH PATTERN:

1START POLARITY OF PULSE (FROM VPOL IN SEQUENCE REGISTERS).

2FIRST TOGGLE POSITION (FROM V-PATTERN REGISTERS).

3SECOND TOGGLE POSITION (FROM V-PATTERN REGISTERS).

4ACTIVE LINE FOR VSG PULSES WITHIN THE FIELD (FROM FIELD REGISTERS).

05

89

1-

05

1

Figure 51. Vertical Sensor Gate Pulse Placement

相关PDF资料 |

PDF描述 |

|---|---|

| VI-JN3-IY-F1 | CONVERTER MOD DC/DC 24V 50W |

| VI-JN2-IZ-B1 | CONVERTER MOD DC/DC 15V 25W |

| VI-JN2-IY-F4 | CONVERTER MOD DC/DC 15V 50W |

| VI-JN2-IY-F3 | CONVERTER MOD DC/DC 15V 50W |

| AD22050NZ | IC AMP DIFF SGL SUPPLY 8-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9992BBCZRL | 功能描述:IC CCD SGNL PROC 12BIT 105CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD9993BBCZ | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1 |

| AD9993BBCZRL | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1,500 |

| AD9993-EBZ | 功能描述:EVAL BOARD MXFE AD9993 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD9994 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Generator |

发布紧急采购,3分钟左右您将得到回复。