- 您现在的位置:买卖IC网 > PDF目录11652 > AD9992BBCZ (Analog Devices Inc)IC CCD SGNL PROC 12BIT 105CSPBGA PDF资料下载

参数资料

| 型号: | AD9992BBCZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 76/92页 |

| 文件大小: | 0K |

| 描述: | IC CCD SGNL PROC 12BIT 105CSPBGA |

| 产品变化通告: | AD9992 Discontinuation 22/Feb/2012 |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,12 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 27mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 105-LFBGA,CSPBGA |

| 供应商设备封装: | 105-CSPBGA(8x8) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

AD9992

Rev. C | Page 78 of 92

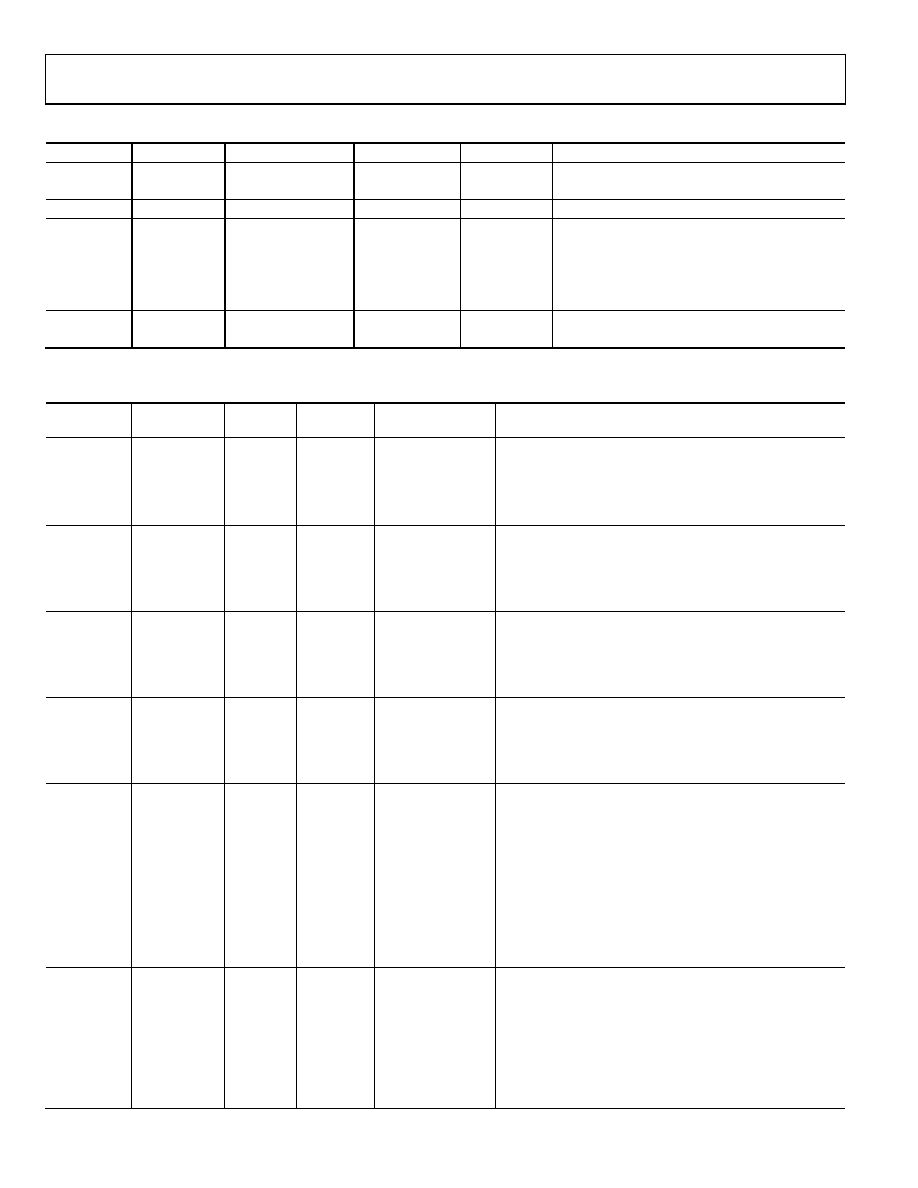

Table 33. Memory Configuration and MODE Registers

Address

Data Bits

Default Value

Update Type

Mnemonic

Description

0x28

[4:0]

0

SCK

VPATNUM

Total number of V-pattern groups.

[9:5]

0

SEQNUM

Total number of V-sequences.

0x2A

[2:0]

0

SCK

MODE

Total number of fields in MODE.

0x2B

[4:0]

0

SCK

FIELD0

Selected first field in MODE.

[9:5]

0

FIELD1

Selected second field in MODE.

[14:10]

0

FIELD2

Selected third field in MODE.

[19:15]

0

FIELD3

Selected fourth field in MODE.

[24:20]

0

FIELD4

Selected fifth field in MODE.

0x2C

[4:0]

0

SCK

FIELD5

Selected sixth field in MODE.

[9:5]

0

FIELD6

Selected seventh field in MODE.

Table 34. Timing Core Registers

Address

Data Bits

Default

Value

Update

Type

Mnemonic

Description

0x30

[5:0]

0

SCK

H1POSLOC

H1 rising edge location.

[13:8]

20

H1NEGLOC

H1 falling edge location.

[16]

1

H1POL

H1 polarity control:

0: Inverse of Figure 19.

1: No inversion.

0x31

[5:0]

0

SCK

H2POSLOC

H2 rising edge location (H5 in HCLK Mode 3).

[13:8]

20

H2NEGLOC

H2 falling edge location (H5 in HCLK Mode 3).

[16]

1

H2POL

H2 polarity (H5 in HCLK Mode 3):

0: Inverse of Figure 19.

1: No inversion.

0x32

[5:0]

0

SCK

HLPOSLOC

HL rising edge location.

[13:8]

20

HLNEGLOC

HL falling edge location.

[16]

1

HLPOL

HL polarity control:

0: Inverse of Figure 19.

1: No inversion.

0x33

[5:0]

0

SCK

RGPOSLOC

RG rising edge location.

[13:8]

10

RGNEGLOC

RG falling edge location.

[16]

1

RGH2POL

RG polarity control:

0: Inverse of Figure 19.

1: No inversion.

0x34

[0]

0

SCK

H1HBLKRETIME

Retime H1, H2, HL HBLK to the internal clock:

0: No retime.

1: Retime.

[1]

0

H2HBLKRETIME

Recommended setting is retime enabled (1). Setting to 1

adds one cycle delay to programmed HBLK positions.

[2]

0

HLHBLKRETIME

[3]

0

HL_HBLK_EN

Enable HBLK for HL output:

0: Disable.

1: Enable.

[7:4]

4

HCLK_WIDTH

Enables wide H-clocks during HBLK interval. Set to 0 to

disable.

0x35

[2:0]

1

SCK

H1DRV

H1 drive strength:

0: Off.

1: 4.3 mA.

2: 8.6 mA.

3: 12.9 mA.

4: 4.3 mA.

5: 8.6 mA.

6: 12.9 mA.

7: 17.2 mA.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-JN3-IY-F1 | CONVERTER MOD DC/DC 24V 50W |

| VI-JN2-IZ-B1 | CONVERTER MOD DC/DC 15V 25W |

| VI-JN2-IY-F4 | CONVERTER MOD DC/DC 15V 50W |

| VI-JN2-IY-F3 | CONVERTER MOD DC/DC 15V 50W |

| AD22050NZ | IC AMP DIFF SGL SUPPLY 8-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9992BBCZRL | 功能描述:IC CCD SGNL PROC 12BIT 105CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件 |

| AD9993BBCZ | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1 |

| AD9993BBCZRL | 功能描述:IC MIXED-SIGNAL FRONT END 196BGA 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 类型:ADC,DAC 输入类型:LVDS 输出类型:LVDS 接口:SPI 电流 - 电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:196-LFBGA,CSPBGA 供应商器件封装:196-CSPBGA(12x12) 标准包装:1,500 |

| AD9993-EBZ | 功能描述:EVAL BOARD MXFE AD9993 制造商:analog devices inc. 系列:* 零件状态:在售 标准包装:1 |

| AD9994 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Bit CCD Signal Processor with Precision Timing Generator |

发布紧急采购,3分钟左右您将得到回复。