- 您现在的位置:买卖IC网 > PDF目录170341 > CXA3266Q PHASE LOCKED LOOP, 0.12 MHz, PQFP48 PDF资料下载

参数资料

| 型号: | CXA3266Q |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, 0.12 MHz, PQFP48 |

| 封装: | PLASTIC, QFP-48 |

| 文件页数: | 39/62页 |

| 文件大小: | 929K |

| 代理商: | CXA3266Q |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

CXA3266Q

- 44 -

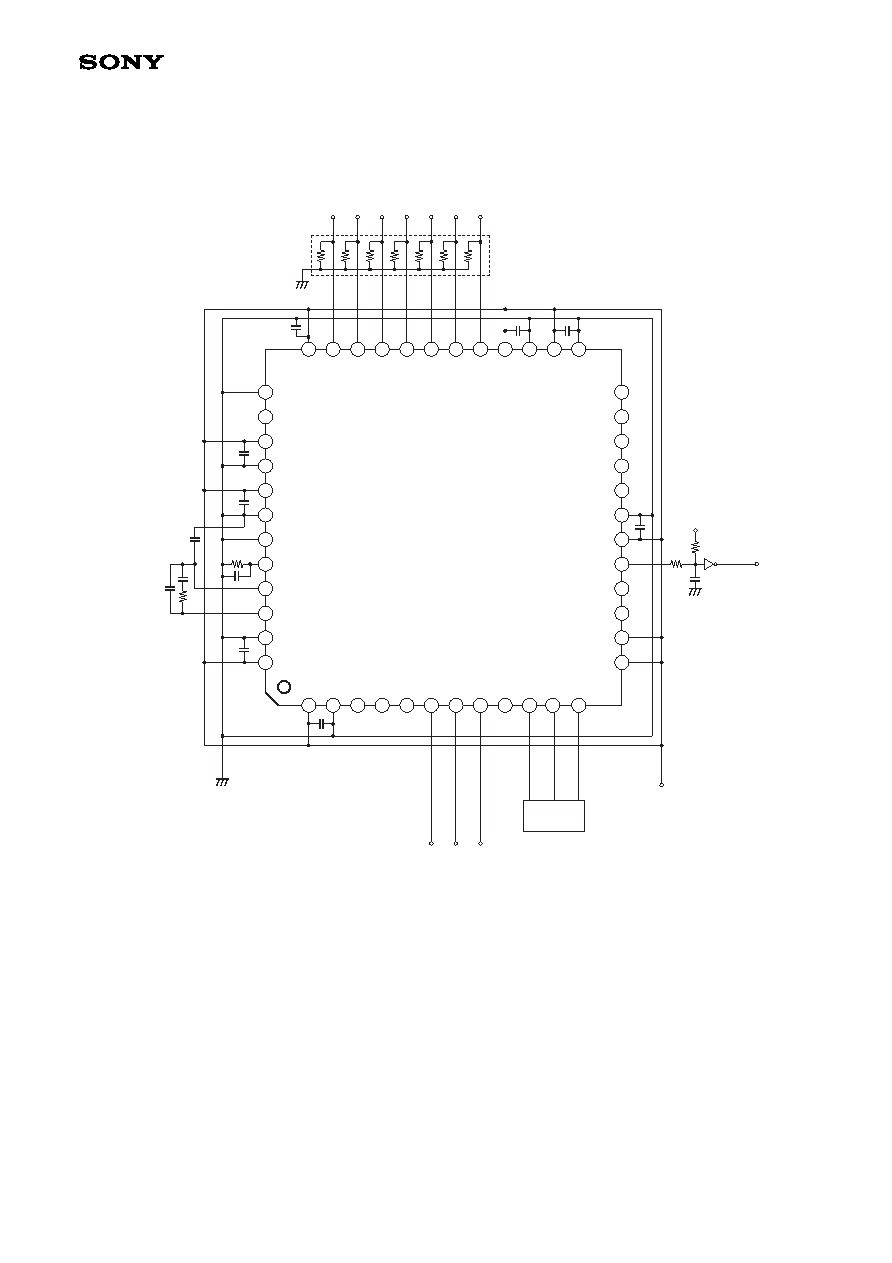

1. Recommended PECL I/O circuit

The peripheral circuits mainly use PECL for digital input and output. Of course, PECL and TTL can also be mixed.

In this case, disable the TTL outputs with the control registers.

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

9

10

3

VCC (+5.0V)

Control

Register

HOLD

SYNCH, SYNCL: PECL

level complementary input

100pF

0.068F

3.0k

680pF

Loop Filter 4

3.0k

100

VCC

UNLOCK output2

GND

100k

10nF

PECL level output pins

330

GND

IOV

CC

IOGND

VCOH

VCOL

VCO

HOLD

SYNCH

SYNCL

SYNC

SENABLE

SCLK

SDATA

PECLV

CC

VBB

DSYNCH

DSYNCL

CLKH

CLKL

CLK/2H

CLK/2L

PECLV

CC

IOGND

TTLV

CC

TTLGND DSYNC

CLK

CLKN

CLK/2

CLK/2N

DGND

DVCC

UNLOCK

DIVOUT

SEROUT

CS

TLOAD

IOGND

VOCLP

PLLVCC

PLLGND

VCOVCC

VCOGND

VCOHGND

IREF

RC2

RC1

IRGND

IRVCC

Notes)

1 Unless otherwise specified, all capacitors are 0.1F.

2 Vary the external resistor and capacitor values of the

UNLOCK output as necessary.

3 This external resistor (3.0k) should be a metal film

resistor in consideration of temperature characteristics.

4 The loop filter's capacitors and resistor should also be

temperature compensated.

GND

相关PDF资料 |

PDF描述 |

|---|---|

| CXA3621GE | SPECIALTY ANALOG CIRCUIT, PBGA30 |

| CXB1140Q | 1000 SERIES, LOW LEVEL TRIGGERED D LATCH, COMPLEMENTARY OUTPUT, MQFP32 |

| CXK77B3640GB-4 | 128K X 36 LATE-WRITE SRAM, 5.3 ns, PBGA119 |

| CXK77P18L80AGB-4A | 512K X 18 LATE-WRITE SRAM, 3.8 ns, PBGA119 |

| CXO-199-148.5MHZ | CRYSTAL OSCILLATOR, SINE OUTPUT, 148.5 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CXA3268AR | 制造商:SONY 制造商全称:Sony Corporation 功能描述:Driver/Timing Generator for Color LCD Panels |

| CXA3271AGE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Fingerprint Sensor |

| CXA3271GE | 制造商:SONY 制造商全称:Sony Corporation 功能描述:Fingerprint Sensor |

| CXA3272R | 制造商:SONY 制造商全称:Sony Corporation 功能描述:CXA3272R |

| CXA3275Q | 制造商:SONY 制造商全称:Sony Corporation 功能描述:PLL/OSC/MIX IC for Digital Tuner |

发布紧急采购,3分钟左右您将得到回复。