- 您现在的位置:买卖IC网 > PDF目录11562 > DS3112+W (Maxim Integrated Products)IC MUX T3/E3 3.3V 256-PBGA PDF资料下载

参数资料

| 型号: | DS3112+W |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 78/133页 |

| 文件大小: | 0K |

| 描述: | IC MUX T3/E3 3.3V 256-PBGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 40 |

| 控制器类型: | 调帧器,多路复用器 |

| 接口: | 并行/串行 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 电流 - 电源: | 150mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-PBGA(27x27) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页当前第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页

DS3112

49 of 133

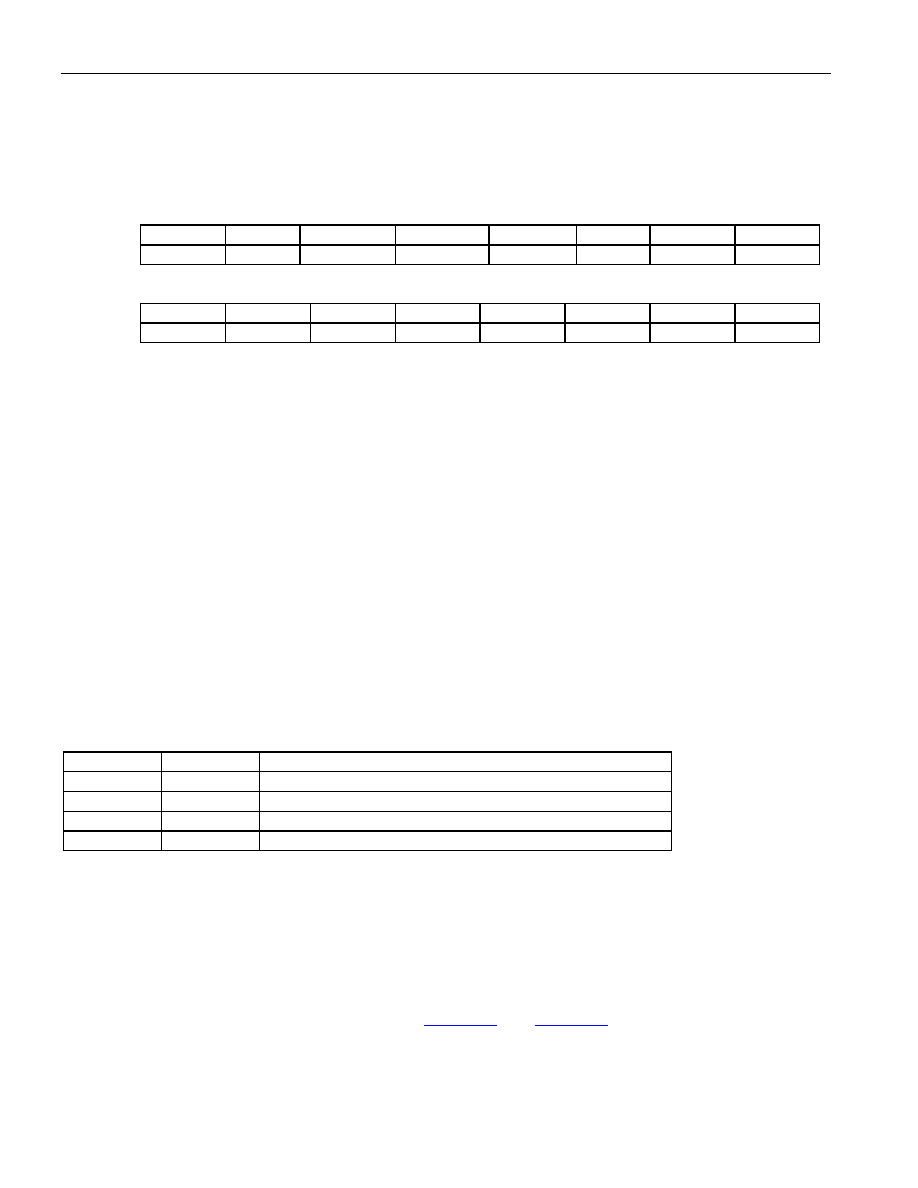

5.4 T3/E3 Framer Control Register Description

Register Name:

T3E3CR

Register Description:

T3/E3 Control Register

Register Address:

10h

Bit #

7

6

5

4

3

2

1

0

Name

DLB

LLB

T3IDLE

E3SnC1

E3SnC0

TPT

TRAI

TAIS

Default

0

Bit #

15

14

13

12

11

10

9

8

Name

—

PLB

TFEBE

AFEBED

ECC

FECC1

FECC0

E3CVE

Default

—

0

Bit 0: T3/E3 Transmit Alarm Indication Signal (TAIS). When this bit is set high in the T3 mode, the transmitter

will generate a properly F-bit and M-bit framed 101010... data pattern with both X bits set to one, all C bits set to

zero, and the proper P bits. This is true regardless of whether the device is in the C-Bit Parity mode or not. When

this bit is set high in the E3 mode, the transmitter will generate an unframed all ones. When this bit it set low,

normal data is transmitted.

0 = do not transmit AIS

1 = transmit AIS

Bit 1: T3/E3 Transmit Remote Alarm Indication (TRAI). When this bit is set high in the T3 mode, both X bits

will be set to a zero. When this bit is set high in the E3 mode, the RAI bit (bit number 11 of each E3 frame) will be

set to a one. When this bit it set low in the T3 mode, both X bits will be set to one. When this bit is set low in the

E3 mode, the RAI bit will be set to a zero.

0 = do not transmit RAI

1 = transmit RAI

Bit 2: T3/E3 Transmit Pass Through Enable (TPT).

0 = enable the framer to insert framing and overhead bits

1 = framer will not insert any framing or overhead bits

Bits 3 and 4: E3 National Bit Control Bits 0 and 1 (E3SnC0 and E3SnC1). These bits determine from where the

E3 national bit is sourced. On the receive side, the Sn bit is always routed to the T3E3INFO Register as well as the

HDLC controller and the FEAC controller. These bits are ignored in the T3 mode.

E3SnC1

E3SnC0

SOURCE OF THE E3 NATIONAL BIT (Sn)

0

Force the Sn bit to one

0

1

Use the HDLC controller to source the Sn bit

1

0

Use the FEAC controller to source the Sn bit

1

Force the Sn bit to zero

Bit 5: Transmit T3 Idle Signal Enable (T3IDLE). When this bit is set high, the T3 Idle Signal will be transmitted

instead of the normal transmit data. The T3 Idle Signal is defined as a normally T3 framed pattern (i.e., with the

proper F bits and M bits along with the proper P bits) where the information bit fields are completely filled with a

data pattern of ...1100... and the C bits in Subframe 3 are set to zero and both X bits are set to one. This bit is

ignored in the E3 mode.

0 = transmit data normally

1 = transmit T3 Idle Signal

Bit 6: T3/E3 Line Loopback Enable (LLB). See Figure 1-1 and Figure 1-2 for a visual description of this

loopback.

0 = disable loopback

1 = enable loopback

相关PDF资料 |

PDF描述 |

|---|---|

| CONREVSMA007-R58 | CONN RP-SMA MALE END CRIMP RG-58 |

| DS26401NA2+ | IC OCTAL FRAMER T1/E1/J1 256BGA |

| VI-24L-IX-S | CONVERTER MOD DC/DC 28V 75W |

| DS26401+ | IC OCTAL FRAMER T1/E1/J1 256BGA |

| PIC16LF1938-E/SS | MCU 8BIT 16K FLASH 28SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3116MP000 | 制造商:Thomas & Betts 功能描述:MAXGARD - RR8F |

| DS311X | 功能描述:KWIK-CHG DESIGNATION STRIPS DBL RoHS:是 类别:盒,外壳,支架 >> 插线台,插座面板 - 配件 系列:Kwik-Change® 标准包装:50 系列:- 附件类型:模拟插头,双 样式:耳机,0.173" 直径 包括:- |

| DS312 | 功能描述:插线板 DESIGN STRIP COVER RoHS:否 制造商:Switchcraft 产品类型:Bantam (TT) 正规化: 高度/机架数量: 深度: 端接类型: 位置/触点数量:48 |

| DS-312 | 制造商:MA-COM 制造商全称:M/A-COM Technology Solutions, Inc. 功能描述:Four-Way Power Divider, 10 - 500 MHz |

| DS312_09 | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-3E FPGA Family: Introduction and Ordering Information |

发布紧急采购,3分钟左右您将得到回复。