- 您现在的位置:买卖IC网 > PDF目录385639 > MT48LC1M16A1S (Micron Technology, Inc.) SYNCHRONOUS DRAM PDF资料下载

参数资料

| 型号: | MT48LC1M16A1S |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | SYNCHRONOUS DRAM |

| 中文描述: | 同步DRAM |

| 文件页数: | 24/51页 |

| 文件大小: | 1480K |

| 代理商: | MT48LC1M16A1S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页

16Mb: x16 SDRAM

16MSDRAMx16.p65

–

Rev. 8/99

Micron Technology, Inc., reserves the right to change products or specifications without notice.

1999, Micron Technology, Inc.

24

16Mb: x16

SDRAM

CLK

DQ

T2

T1

T4

T3

T6

T5

T0

COMMAND

WRITE - AP

BANK

n

NOP

NOP

NOP

NOP

D

IN

a

+ 1

D

IN

a

NOP

NOP

T7

BANK

n

BANK

m

ADDRESS

NOTE:

1. DQM is LOW.

BANK

n

,

COL

a

BANK

m

,

COL

d

READ - AP

BANK

m

Internal

States

t

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

Page Active

READ with Burst of 4

t

tRP - BANK

m

D

OUT

d

D

OUT

d

+ 1

CAS Latency = 3 (BANK

m

)

RP - BANK

n

WR - BANK

n

Figure 26

WRITE w ith AUTO PRECHARGE Interrupted by a READ

DON

’

T CARE

CLK

DQ

T2

T1

T4

T3

T6

T5

T0

COMMAND

WRITE - AP

BANK

n

NOP

NOP

NOP

NOP

D

IN

d

+ 1

D

IN

d

D

IN

a

+ 1

D

IN

a

+ 2

D

IN

a

D

IN

d

+ 2

D

IN

d

+ 3

NOP

T7

BANK

n

BANK

m

ADDRESS

NOP

NOTE:

1. DQM is LOW.

BANK

n

,

COL

a

BANK

m

,

COL

d

WRITE - AP

BANK

m

Internal

States

t

Page Active

WRITE with Burst of 4

Interrupt Burst, Write-Back

Precharge

Page Active

WRITE with Burst of 4

Write-Back

WR - BANK

n

tRP - BANK

n

tWR - BANK

m

Figure 27

WRITE w ith AUTO PRECHARGE Interrupted by a WRITE

WRITE with AUTO PRECHARGE

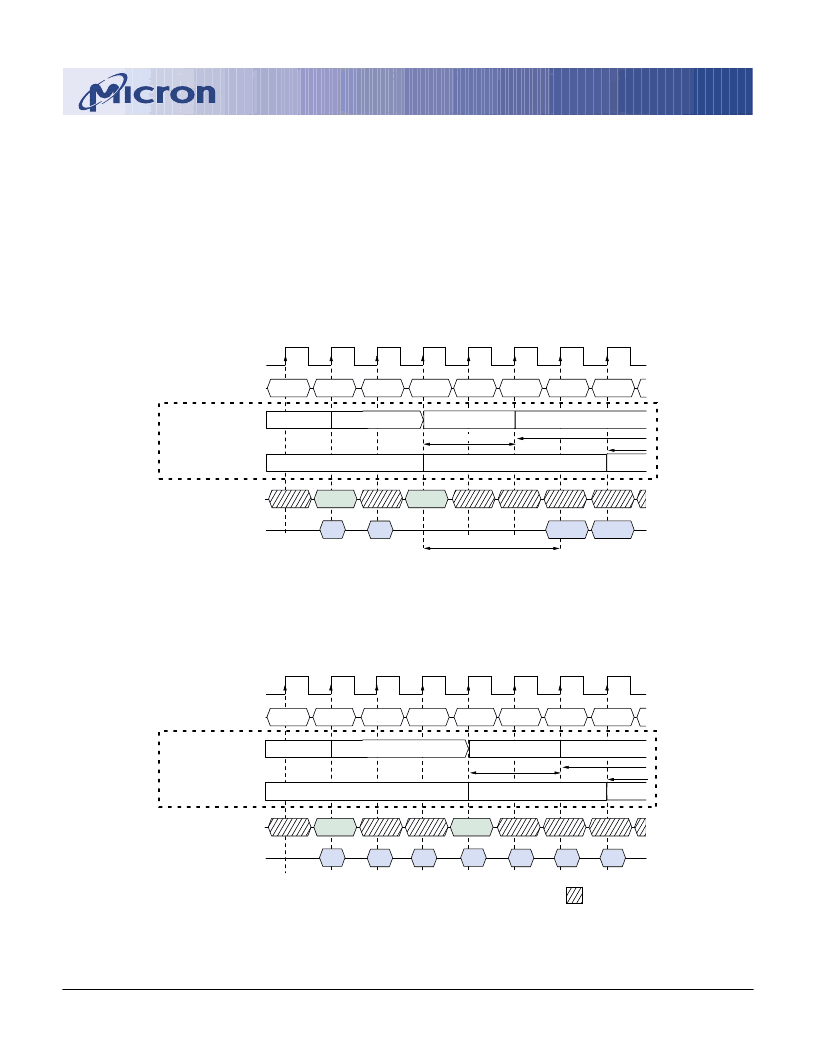

3. Interrupted by a READ (with or without AUTO

PRECHARGE): A READ to bank m will interrupt a

WRITE on bank n when registered, with the data-

out appearing CAS latency later. The PRECHARGE

to bank n will begin after

t

WR is met, where

t

WR

begins when the READ to bank m is registered. The

last valid WRITE to bank n will be data-in registered

one clock prior to the READ to bank m (Figure 26).

4. Interrupted by a WRITE (with or without AUTO

PRECHARGE): A WRITE to bank m will interrupt a

WRITE on bank n when registered. The PRECHARGE

to bank n will begin after

t

WR is met, where

t

WR

begins when the WRITE to bank m is registered. The

last valid data WRITE to bank n will be data regis-

tered one clock prior to a WRITE to bank m (Figure

27).

相关PDF资料 |

PDF描述 |

|---|---|

| MT48LC2M32LFFC | 512K x 32 x 4 banks 3.3v SDRAM(3.3V,512K x 32 x 4组同步动态RAM) |

| MT48LC4M16A2 | SYNCHRONOUS DRAM |

| MT48LC16M4A2 | RSD Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 24V; Output Voltage (Vdc): 3.3V; Power: 1W; 1kVDC and 3kVDC Isolation Options; Approved for Medical Applications; Suitable for Automated Assembly; 8, 10 and 12 pin Pinning Style Options; Optional Continuous Short Circuit Protected; Efficiency to 85% |

| MT48LC8M16A2 | SYNCHRONOUS DRAM |

| MT48V2M32LFFC | 512K x 32 x 4 banks 2.5V SDRAM(2.5V,512K x 32 x 4组同步动态RAM) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT48LC1M16A1-TG | 制造商:Micron Technology Inc 功能描述: |

| MT48LC1M16A1TG6SE | 制造商:MICRON 功能描述:New |

| MT48LC1M16A1TG-6SE | 制造商:Micron Technology Inc 功能描述:IC,SDRAM,2X512KX16,CMOS,TSOP,50PIN,PLASTIC |

| MT48LC1M16A1TG-7S | 制造商:Mitel Networks Corporation 功能描述:SDRAM, 1M x 16, 50 Pin, Plastic, TSOP |

| MT48LC1M16A1TG-7SE | 制造商:Micron Technology Inc 功能描述:SDRAM, 1M x 16, 50 Pin, Plastic, TSOP |

发布紧急采购,3分钟左右您将得到回复。