- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50114GAG2 (XILINX INC) SPECIALTY TELECOM CIRCUIT, PBGA552 PDF资料下载

参数资料

| 型号: | ZL50114GAG2 |

| 厂商: | XILINX INC |

| 元件分类: | 通信及网络 |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| 封装: | 35 X 35 MM, 1.27 MM PITCH, LEAD FREE, PLASTIC, MS-034, BGA-552 |

| 文件页数: | 58/113页 |

| 文件大小: | 2004K |

| 代理商: | ZL50114GAG2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页

ZL50110/11/12/14

Data Sheet

49

Zarlink Semiconductor Inc.

3.7

Test Facilities

3.7.1

Administration, Control and Test Interface

All Administration, Control and Test Interface signals are 5 V tolerant.

3.7.2

JTAG Interface

All JTAG Interface signals are 5 V tolerant, and conform to the requirements of IEEE1149.1 (2001).

The ZL50111 and ZL50112 share a common JTAG ID. They also share a common CHIP_ID register value.

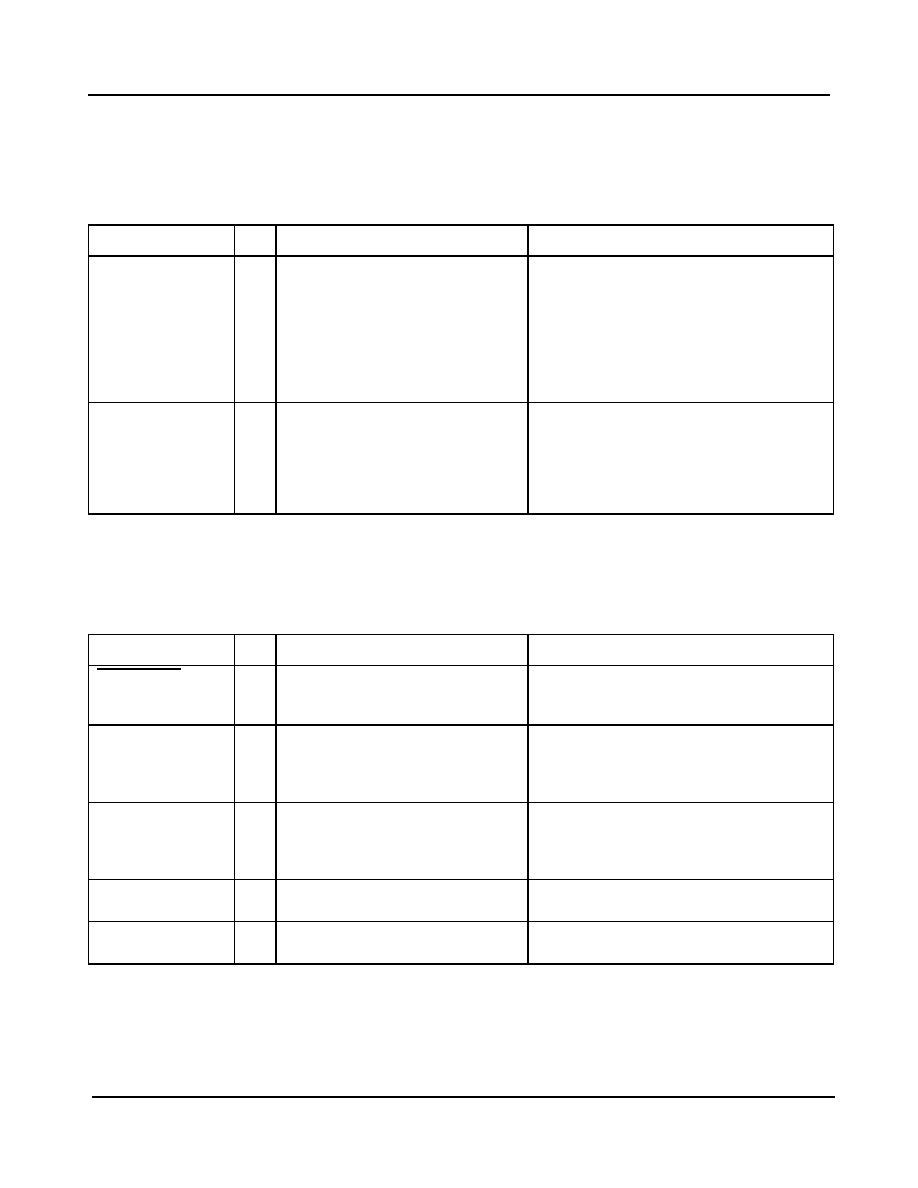

Signal

I/O

Package Balls

Description

GPIO[15:0]

ID/

OT

[15]

AA4

[7]

AA2

[14]

AB3

[6]

Y3

[13]

AC2

[5]

AB1

[12]

AC1

[4]

Y2

[11]

AB2

[3]

W4

[10]

Y4

[2]

V5

[9]

W5

[1]

AA1

[8]

AA3

[0]

W3

General Purpose I/O pins. Connected to an

internal register, so customer can set

user-defined parameters. Bits [4:0] reserved

at startup or reset for memory Tapped Delay

Line (TDL) setup. See the ZL50110/11/12/14

Programmers Model for more details.

Recommend 5 kohm pulldown on these

signals.

TEST_MODE[2:0]

I D

[2]

AF6

[1]

AB9

[0]

AC8

Test Mode input - ensure these pins are tied

to ground for normal operation.

000 SYS_NORMAL_MODE

001-010 RESERVED

011 SYS_TRISTATE_MODE

100-111 RESERVED

Table 17 - Administration/Control Interface Package Ball Definition

Signal

I/O

Package Balls

Description

JTAG_TRST

I U

AE7

JTAG Reset. Asynchronous reset. In normal

operation this pin should be pulled low.

Recommend external pull-down.

JTAG_TCK

I

AD8

JTAG Clock - maximum frequency is

25 MHz, typically run at 10 MHz. In normal

operation this pin should be pulled either

high or low. Recommend external pull-down.

JTAG_TMS

I U

AA10

JTAG test mode select. Synchronous to

JTAG_TCK rising edge. Used by the Test

Access Port controller to set certain test

modes.

JTAG_TDI

I U

AF7

JTAG test data input. Synchronous to

JTAG_TCK.

JTAG_TDO

O

AC9

JTAG test data output. Synchronous to

JTAG_TCK.

Table 18 - JTAG Interface Package Ball Definition

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50233/GDG | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50408GDC | DATACOM, LAN SWITCHING CIRCUIT, PBGA208 |

| ZL50408GDG2 | DATACOM, LAN SWITCHING CIRCUIT, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL50115 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50115GAG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 1K X 1K 1.8V/3.3V 324BGA - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50115GAG2 | 制造商:Microsemi Corporation 功能描述:PB FREE 1 TDM + 1 ETHERNET - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50116 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50116GAG | 制造商:Microsemi Corporation 功能描述:2 TDM + 1 ETHERNET - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

发布紧急采购,3分钟左右您将得到回复。