- 您现在的位置:买卖IC网 > PDF目录300164 > ZL50114GAG2 (XILINX INC) SPECIALTY TELECOM CIRCUIT, PBGA552 PDF资料下载

参数资料

| 型号: | ZL50114GAG2 |

| 厂商: | XILINX INC |

| 元件分类: | 通信及网络 |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| 封装: | 35 X 35 MM, 1.27 MM PITCH, LEAD FREE, PLASTIC, MS-034, BGA-552 |

| 文件页数: | 72/113页 |

| 文件大小: | 2004K |

| 代理商: | ZL50114GAG2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页

ZL50110/11/12/14

Data Sheet

61

Zarlink Semiconductor Inc.

5.3.3

TDM Clock Structure

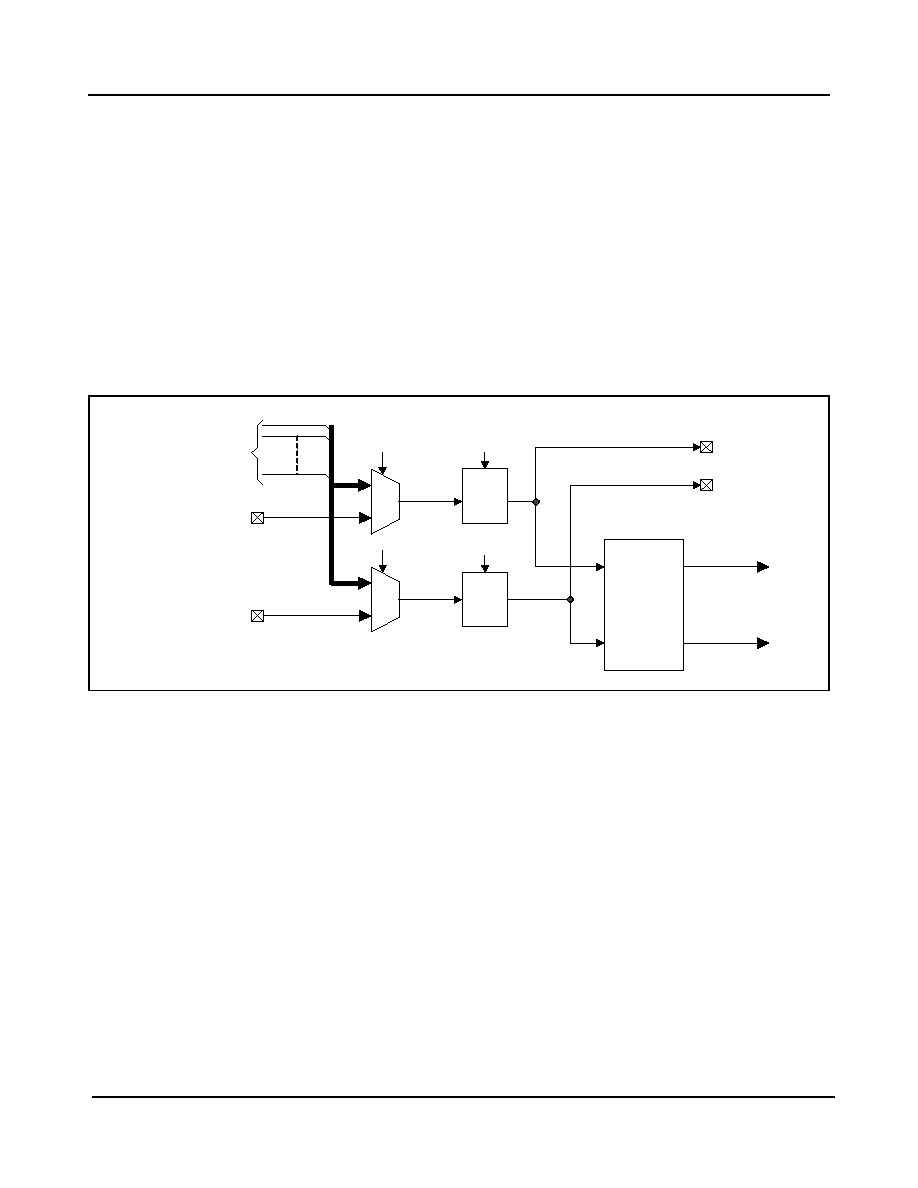

The TDM interface can operate in two modes, synchronous for structured TDM data, and asynchronous for

unstructured TDM data. The ZL50110/11/12/14 is capable of providing the TDM clock for either of the modes. The

ZL50110/11/12/14 supports clock recovery in both synchronous and asynchronous modes of operation. In

asynchronous operation each stream may have independent clock recovery.

5.3.3.1

Synchronous TDM Clock Generation

In synchronous mode all 32 streams will be driven by a common clock source. When the ZL50110/11/12/14 is

acting as a master device, the source can either be the internal DPLL or an external PLL. In both cases, the primary

and secondary reference clocks are taken from either two TDM input clocks, or two external clock sources driven to

the chip. The input clocks are then divided down where necessary and sent either to the internal DPLL or to the

output pins for connection to an external DPLL. The DPLL then provides the common clock and frame pulse

required to drive the TDM streams. See “DPLL Specification” on page 75 for further details.

Figure 14 - Synchronous TDM Clock Generation

When the ZL50110/11/12/14 is acting as a slave device, the common clock and frame pulse signals are taken from

an external device providing the TDM master function.

5.3.3.2

Asynchronous TDM Clock Generation

Each stream uses a separate internal DCO to provide an asynchronous TDM clock output. The DCO can be

controlled to recover the clock from the original TDM source depending on the timing algorithm used.

5.4

Payload Assembly

Data traffic received on the TDM Access Interface is sampled in the TDM Interface block, and synchronized to the

internal clock. It is then forwarded to the payload assembly process. The ZL50110/11/12/14 Payload Assembler can

handle up to 128 active packet streams or “contexts” simultaneously. Packet payloads are assembled in the format

shown in Figure 15 - on page 62. This meets the requirements of the IETF CESoPSN standard (RFC 5086).

Alternatively, packet payloads are assembled in the format shown in Figure 17 - on page 63. This meets the

requirements of the IETF SAToP standard (RFC 4553).

The Packet Transmit (PTX) circuit adds Layer 2 and Layer 3 protocol headers. The chosen protocol header

combination for addition by the PTX must not exceed 64 bytes. The exception is context 127 (the 128th context),

which must not exceed 56 bytes.

FRAME

CLOCK

TDM_CLKi[31:0]

PLL_SE

C

PLL_PRI

SRS

SRD

DIV

Internal

DPLL

PRS

PRD

TDM_CLKiP

TDM_CLKiS

相关PDF资料 |

PDF描述 |

|---|---|

| ZL50114GAG | SPECIALTY TELECOM CIRCUIT, PBGA552 |

| ZL50232GD | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50233/GDG | DATACOM, ISDN ECHO CANCELLER, PBGA208 |

| ZL50408GDC | DATACOM, LAN SWITCHING CIRCUIT, PBGA208 |

| ZL50408GDG2 | DATACOM, LAN SWITCHING CIRCUIT, PBGA208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL50115 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50115GAG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 1K X 1K 1.8V/3.3V 324BGA - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50115GAG2 | 制造商:Microsemi Corporation 功能描述:PB FREE 1 TDM + 1 ETHERNET - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50116 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50116GAG | 制造商:Microsemi Corporation 功能描述:2 TDM + 1 ETHERNET - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

发布紧急采购,3分钟左右您将得到回复。