- 您现在的位置:买卖IC网 > PDF目录20639 > ADE7878ACPZ (Analog Devices Inc)IC ENERGY METERING 3PH 40LFCSP PDF资料下载

参数资料

| 型号: | ADE7878ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 62/100页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METERING 3PH 40LFCSP |

| 标准包装: | 1 |

| 输入阻抗: | 400 千欧 |

| 测量误差: | 0.2% |

| 电压 - 高输入/输出: | 2.4V |

| 电压 - 低输入/输出: | 0.4V |

| 电源电压: | 2.4 V ~ 3.7 V |

| 测量仪表类型: | 3 相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

�� �

�

�

�10� 3�

�MC� [� imp/kwh� ]� � 10� n�

�CFCYC� =� 2�

�ADE7854/ADE7858/ADE7868/ADE7878�

�By� default,� the� TERMSELx� bits� are� all� 1� and� the� CF1SEL� bits� are�

�000,� the� CF2SEL� bits� are� 001,� and� the� CF3SEL� bits� are� 010.� This�

�means� that� by� default,� the� CF1� digital-to-frequency� converter�

�produces� signals� proportional� to� the� sum� of� all� 3-phase� total�

�active� powers,� CF2� produces� signals� proportional� to� total�

�reactive� powers,� and� CF3� produces� signals� proportional� to�

�apparent� powers.�

�Similar� to� the� energy� accumulation� process,� the� energy-to-�

�frequency� conversion� is� accomplished� in� two� stages.� In� the� first�

�stage,� the� instantaneous� phase� powers� obtained� from� the� DSP� at�

�the� 8� kHz� rate� are� shifted� left� by� seven� bits� and� then� accumulate�

�into� an� internal� register� at� a� 1� MHz� rate.� When� a� threshold� is�

�reached,� a� pulse� is� generated� and� the� threshold� is� subtracted�

�from� the� internal� register.� The� sign� of� the� energy� in� this� moment�

�is� considered� the� sign� of� the� sum� of� phase� powers� (see� the� Sign�

��The� threshold� is� the� same� threshold� used� in� various� active,�

�reactive,� and� apparent� energy� accumulators� in� the� DSP,� such�

�as� the� WTHR,� VARTHR,� or� VATHR� registers,� except� for� being�

�shifted� left� by� seven� bits.� The� advantage� of� accumulating� the�

�instantaneous� powers� at� the� 1� MHz� rate� is� that� the� ripple� at� the�

�CFx� pins� is� greatly� diminished.�

�The� second� stage� consists� of� the� frequency� divider� by� the�

�CFxDEN� 16-bit� unsigned� registers.� The� values� of� CFxDEN�

�depend� on� the� meter� constant� (MC),� measured� in� impulses/kWh�

�and� how� much� energy� is� assigned� to� one� LSB� of� various� energy�

�registers:� xWATTHR,� xVARHR,� and� so� forth.� Supposing� a� deri-�

�vative� of� wh� [10� n� wh],� n� a� positive� or� negative� integer,� is� desired�

�as� one� LSB� of� xWATTHR� register.� Then,� CFxDEN� is� as� follows:�

�CFxDEN� =� (46)�

�The� derivative� of� wh� must� be� chosen� in� such� a� way� to� obtain� a�

�CFxDEN� register� content� greater� than� 1.� If� CFxDEN� =� 1,� then�

�the� CFx� pin� stays� active� low� for� only� 1� μs,� therefore,� avoid� this�

�number.� The� frequency� converter� cannot� accommodate� fractional�

�results;� the� result� of� the� division� must� be� rounded� to� the� nearest�

�integer.� If� CFxDEN� is� set� equal� to� 0,� then� the� ADE78xx� considers� it�

�to� be� equal� to� 1.�

�The� pulse� output� for� all� digital-to-frequency� converters� stays�

�low� for� 80� ms� if� the� pulse� period� is� larger� than� 160� ms� (6.25� Hz).� If�

�the� pulse� period� is� smaller� than� 160� ms� and� CFxDEN� is� an� even�

�number,� the� duty� cycle� of� the� pulse� output� is� exactly� 50%.� If� the�

�pulse� period� is� smaller� than� 160� ms� and� CFxDEN� is� an� odd�

�number,� the� duty� cycle� of� the� pulse� output� is�

�(1+1/� CFxDEN� )� � 50%�

�Data� Sheet�

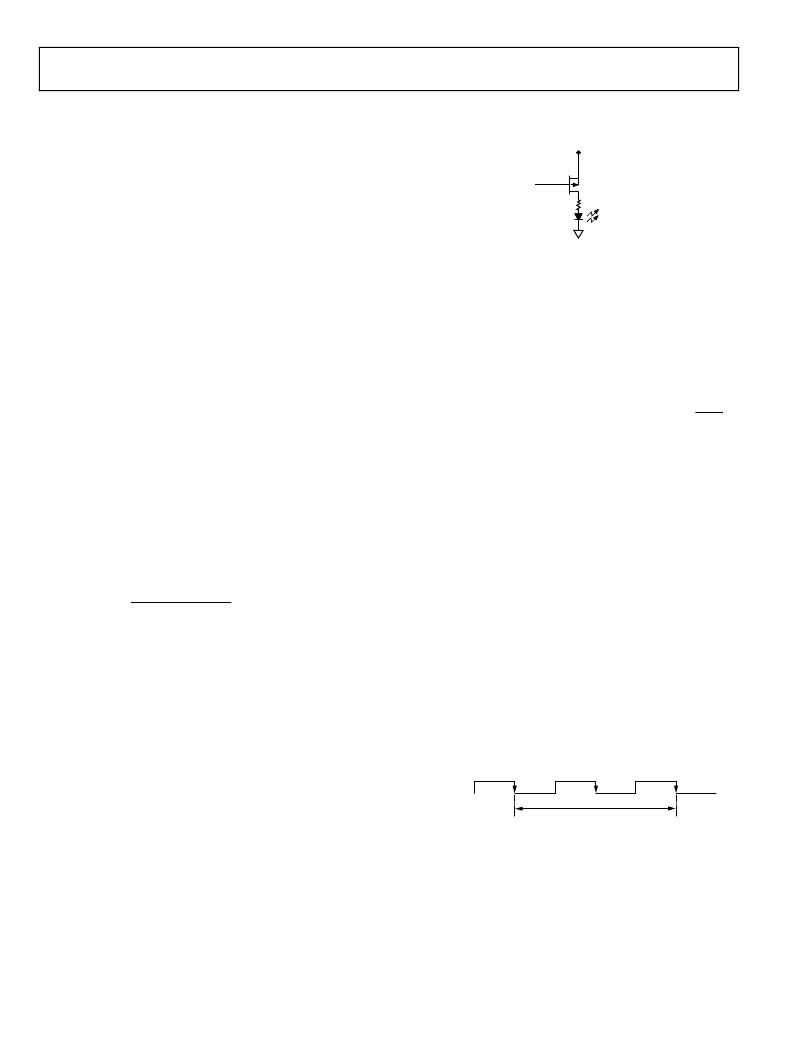

�The� pulse� output� is� active� low� and� preferably� connected� to� an�

��V� DD�

�CFx� PIN�

�Figure� 76.� CFx� Pin� Recommended� Connection�

�Bits[11:9]� (CF3DIS,� CF2DIS,� and� CF1DIS)� of� the� CFMODE�

�register� decide� if� the� frequency� converter� output� is� generated�

�at� the� CF3,� CF2,� or� CF1� pin.� When� Bit� CFxDIS� is� set� to� 1� (the�

�default� value),� the� CFx� pin� is� disabled� and� the� pin� stays� high.�

�When� Bit� CFxDIS� is� cleared� to� 0,� the� corresponding� CFx� pin�

�output� generates� an� active� low� signal.�

�Bits[16:14]� (CF3,� CF2,� CF1)� in� the� Interrupt� Mask� Register� MASK0�

�manage� the� CF3,� CF2,� and� CF1� related� interrupts.� When� the�

�CFx� bits� are� set,� whenever� a� high-to-low� transition� at� the� corres-�

�ponding� frequency� converter� output� occurs,� an� interrupt� IRQ0�

�is� triggered� and� a� status� bit� in� the� STATUS0� register� is� set� to� 1.�

�The� interrupt� is� available� even� if� the� CFx� output� is� not� enabled�

�by� the� CFxDIS� bits� in� the� CFMODE� register.�

�Synchronizing� Energy� Registers� with� CFx� Outputs�

�The� ADE7854� /� ADE7858� /� ADE7868� /� ADE7878� contain� a� feature�

�that� allows� synchronizing� the� content� of� phase� energy� accu-�

�mulation� registers� with� the� generation� of� a� CFx� pulse.� When�

�a� high-to-low� transition� at� one� frequency� converter� output�

�occurs,� the� content� of� all� internal� phase� energy� registers� that�

�relate� to� the� power� being� output� at� CFx� pin� is� latched� into� hour�

�registers� and� then� resets� to� 0.� See� Table� 22� for� the� list� of� registers�

�that� are� latched� based� on� the� CFxSEL[2:0]� bits� in� the� CFMODE�

�register.� All� 3-phase� registers� are� latched� independent� of� the�

�TERMSELx� bits� of� the� COMPMODE� register.� The� process� is�

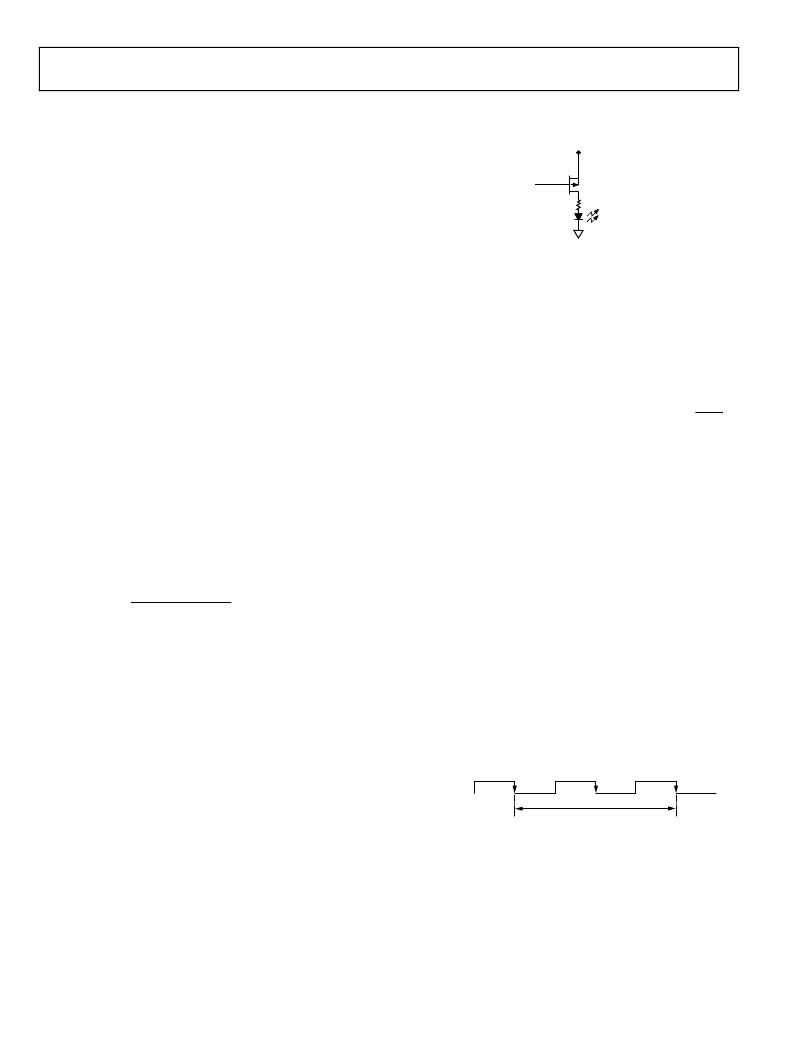

�shown� in� Figure� 77� for� CF1SEL[2:0]� =� 010� (apparent� powers�

�contribute� at� the� CF1� pin)� and� CFCYC� =� 2.�

�The� CFCYC� 8-bit� unsigned� register� contains� the� number� of� high� to�

�low� transitions� at� the� frequency� converter� output� between� two�

�consecutive� latches.� Avoid� writing� a� new� value� into� the� CFCYC�

�register� during� a� high-to-low� transition� at� any� CFx� pin.�

�CF1� PULSE�

�BASED� ON�

�PHASE� A� AND�

�PHASE� B�

�APPARENT�

�POWERS�

�AVAHR,� BVAHR,� AVAHR,� BVAHR,�

�CVAHR� LATCHED� CVAHR� LATCHED�

�ENERGY� REGISTERS� ENERGY� REGISTERS�

�RESET� RESET�

�Figure� 77.� Synchronizing� AVAHR� and� BVAHR� with� CF1�

�Bits[14:12]� (CF3LATCH,� CF2LATCH,� and� CF1LATCH)� of� the�

�CFMODE� register� enable� this� process� when� set� to� 1.� When�

�cleared� to� 0,� the� default� state,� no� latch� occurs.� The� process� is�

�available� even� if� the� CFx� output� is� not� enabled� by� the� CFxDIS�

�bits� in� the� CFMODE� register.�

�Rev.� H� |� Page� 62� of� 100�

�相关PDF资料 |

PDF描述 |

|---|---|

| GBC06DREI-S13 | CONN EDGECARD 12POS .100 EXTEND |

| VI-J60-CX-F4 | CONVERTER MOD DC/DC 5V 75W |

| ECA10DCBT | CONN EDGECARD 20POS R/A .125 SLD |

| EL7242CSZ-T13 | IC DRIVER MOSFET DUAL HS 8-SOIC |

| ADE7169ASTZF16 | IC ENERGY METER 1PHASE 64LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADE7878ACPZ | 制造商:Analog Devices 功能描述:IC MULTIFUNCTION ENERGY METERING LFCSP40 |

| ADE7878ACPZ-RL | 功能描述:IC ENERGY METERING 3PH 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7878XCPZ | 制造商:Analog Devices 功能描述:POLY PHASE MULTIFUNCTION ENERGY METERING IC WITH TOTAL - Bulk |

| ADE7880 | 制造商:Analog Devices 功能描述:BOARD EVAL ENERGY METER ADE |

| ADE7880ACPZ | 功能描述:IC ENERGY METERING 3PH 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

发布紧急采购,3分钟左右您将得到回复。