- 您现在的位置:买卖IC网 > PDF目录189449 > OR4E062BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 2024 CLBS, 515000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | OR4E062BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 2024 CLBS, 515000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 99/151页 |

| 文件大小: | 2680K |

| 代理商: | OR4E062BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页当前第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页

Lattice Semiconductor

51

Data Sheet

September, 2002

ORCA Series 4 FPGAs

Microprocessor Interface (continued)

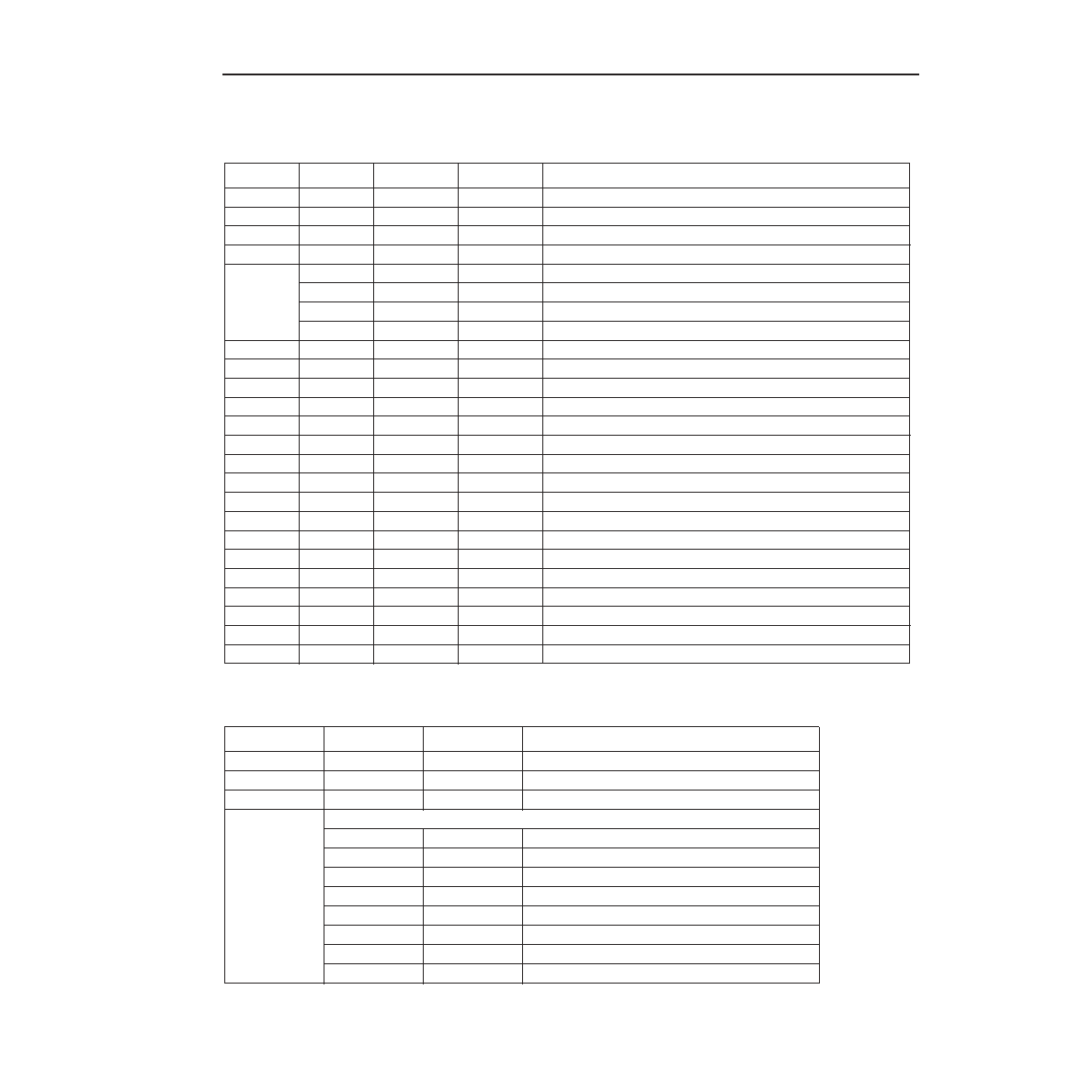

Table 23. Embedded System Bus/MPI Registers

Note: RO = Read Only, R/W = Read/Write

Table 24. Interrupt Register Space Assignments

Note: RO = Read Only, R/W = Read/Write.

For internal system bus, bit 7 is most signicant bit, for MPI bit 0 is most signicant bit.

Register

Byte

Read/Write Initial Value

Description

00

03-00

RO

—

32-bit device ID

01

07-04

R/W

—

Scratchpad register

02

0B-08

R/W

—

Command register

03

0F-0C

RO

—

Status register

04

13

R/W

—

Interrupt enable register – MPI

12

R/W

—

Interrupt enable register – USER

11

R/W

—

Interrupt enable register – FPSC (unused for FPGAs)

10

RO

—

Interrupt cause register

05

17-14

R/W

—

Readback address register (14 bits)

06

1B-18

RO

—

Readback data register

07

1F-1C

R/W

—

Conguration data register

08

23-20

RO

—

Trap address register

09

27-24

RO

—

Bus error address register

0A

2B-28

RO

—

Interrupt vector 1 predened by conguration bit stream

0B

2F-2C

RO

—

Interrupt vector 2 predened by conguration bit stream

0C

33-30

RO

—

Interrupt vector 3 predened by conguration bit stream

0D

37-34

RO

—

Interrupt vector 4 predened by conguration bit stream

0E

3B-38

RO

—

Interrupt vector 5 predened by conguration bit stream

0F

3F-3C

RO

—

Interrupt vector 6 predened by conguration bit stream

10

43—40

—

Top-left PPLL

11

47—44

—

Top-left HPLL

14

53—50

—

Top-right PPLL

18

63—60

—

Bottom-left PPLL

19

67—64

—

Bottom-left HPLL

1C

73—70

—

Bottom-right PPLL

Byte

bit

Read/Write

Description

13

7-0

R/W

Interrupt Enable Register – MPI

12

7-0

R/W

Interrupt Enable Register – USER

11

7-0

R/W

Interrupt Enable Register – FPSC

10

Interrupt Cause Registers

7RO

USER_IRQ_GENERAL;

6RO

USER_IRQ_SLAVE;

5RO

USER_IRQ_MASTER;

4RO

CFG_IRQ_DATA;

3RO

ERR_FLAG 1

2RO

MPI_IRQ

1RO

FPSC_IRQ_SLAVE;

0RO

FPSC_IRQ_MASTER

相关PDF资料 |

PDF描述 |

|---|---|

| OR4E063BA352-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA352 |

| OR4E063BM680-DB | FPGA, 2024 CLBS, 515000 GATES, PBGA680 |

| ORT4622-8BC432I | FPGA, PBGA432 |

| ORT4622-8BM680I | FPGA, PBGA680 |

| ORT4622-8BC432I | FPGA, PBGA432 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR4E10 | 制造商:AGERE 制造商全称:AGERE 功能描述:Field-Programmable Gate Arrays |

| OR4E14 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Gate Arrays |

| OR4E2 | 制造商:AGERE 制造商全称:AGERE 功能描述:Field-Programmable Gate Arrays |

| OR4E2-1BA256 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| OR4E2-1BA352 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。