- 您现在的位置:买卖IC网 > PDF目录69541 > W9725G6IB-18 (WINBOND ELECTRONICS CORP) 16M X 16 DDR DRAM, 0.35 ns, PBGA84 PDF资料下载

参数资料

| 型号: | W9725G6IB-18 |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | 16M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| 封装: | 8 X 12.50 MM, ROHS COMPLIANT, WBGA-84 |

| 文件页数: | 42/69页 |

| 文件大小: | 1644K |

| 代理商: | W9725G6IB-18 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

PRELIMINARY W9725G6IB

Publication Release Date:Nov. 14, 2008

- 47 -

Revision P04

Note:

1. If refresh timing is violated, data corruption may occur and the data must be re-written with valid data before a valid READ

can be executed.

2. This is an optional feature. For detailed information, please refer to “operating temperature condition” chapter 9.2 in this

data sheet.

3. Min. (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device.

4. tCKE min of 3 clocks means CKE must be registered on three consecutive positive clock edges. CKE must remain at the

valid input level the entire time it takes to achieve the 3 clocks of registration. Thus, after any CKE transition, CKE may not

transition from its valid level during the time period of tIS + 2 x tCK + tIH.

5. A minimum of two clocks (2 * tCK) is required irrespective of operating frequency.

6. tDAL = WR + RU{ tRP[nS] / tCK[nS] }, where RU stands for round up. WR refers to the tWR parameter stored in the MRS.

For tRP, if the result of the division is not already an integer, round up to the next highest integer. tCK refers to the

application clock period.

Example: For DDR2-533 at tCK = 3.75nS with WR programmed to 4 clocks.

tDAL = 4 + (15 nS / 3.75 nS) clocks = 4 + (4) clocks = 8 clocks.

7. tWTR is at least two clocks (2 * tCK) independent of operation frequency.

8. This is a minimum requirement. Minimum read to precharge timing is AL + BL/2 providing that the tRTP and tRAS(min) have

been satisfied.

9. The maximum limit for the tWPST parameter is not a device limit. The device operates with a greater value for this parameter,

but system performance (bus turnaround) will degrades accordingly.

10. tDQSQ: Consists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers as

well as output Slew Rate mismatch between DQS / DQS and associated DQ in any given cycle.

11. The tHZ, tRPST and tLZ, tRPRE parameters are referenced to a specific voltage level, which specify when the device output

is no longer driving (tHZ, tPRST), or begins driving (tLZ, tRPRE). tHZ and tLZ transitions occur in the same access time

windows as valid data transitions. These parameters are verified by design and characterization, but not subject to

production test.

12. User can choose which active power down exit timing to use via MRS (bit 12). tXARD is expected to be used for fast active

power down exit timing. tXARDS is expected to be used for slow active power down exit timing.

13. AL = Additive Latency.

14. ODT turn on time min. is when the device leaves high impedance and ODT resistance begins to turn on. ODT turn on time

max. is when the ODT resistance is fully on. Both are measure from tAOND.

15. ODT turn off time min. is when the device starts to turn off ODT resistance. ODT turn off time max. is when the bus is in

high impedance. Both are measured from tAOFD.

16. The clock frequency is allowed to change during Self Refresh mode or precharge power-down mode. In case of clock

frequency change during precharge power-down, a specific procedure is required as described in Chapter 7.10.

17. Tests for AC timing, IDD, and electrical AC and DC characteristics may be conducted at nominal reference/supply voltage

levels, but the related specifications and device operation are guaranteed for the full voltage range specified. ODT is

disabled for all measurements that are not ODT-specific.

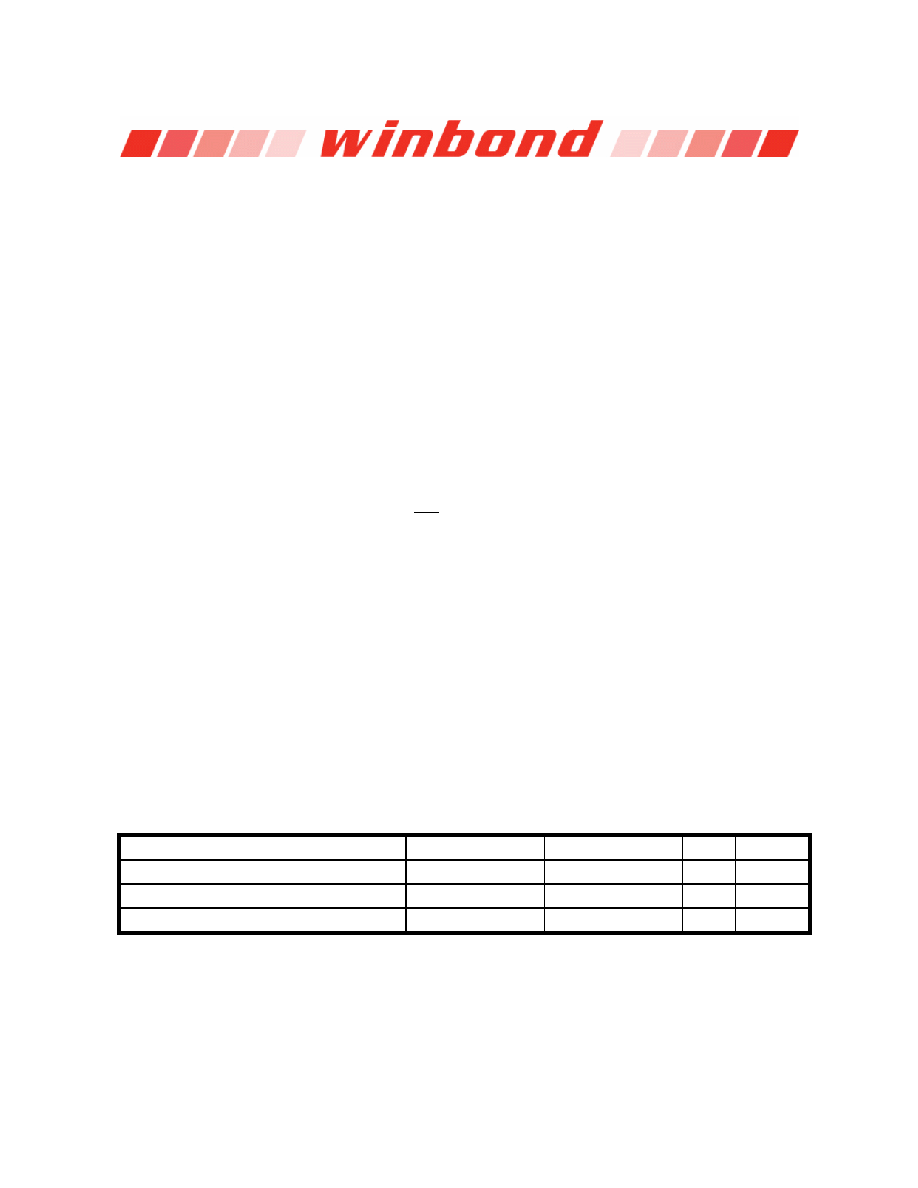

9.12. AC Input Test Conditions

(0

℃ ≤ TCASE ≤ 85℃ for -18/-25/-3, VDD, VDDQ = 1.8V ± 0.1V)

CONDITION

SYMBOL

VALUE

UNIT

NOTES

Input reference voltage

VREF

0.5 x VDDQ

V

1

Input signal maximum peak to peak swing

VSWING(MAX)

1.0

V

1

Input signal minimum slew rate

SLEW

1.0

V/nS

2, 3

Note:

1. Input waveform timing is referenced to the input signal crossing through the VIH/IL(ac) level applied to the device under test.

2. The input signal minimum slew rate is to be maintained over the range from VREF to VIH(ac) min for rising edges and the

range from VREF to VIL(ac) max for falling edges as shown in the below figure.

3. AC timings are referenced with input waveforms switching from VIL(ac) to VIH(ac) on the positive transitions and VIH(ac) to

VIL(ac) on the negative transitions

.

相关PDF资料 |

PDF描述 |

|---|---|

| W9864G6EB-7 | 4M X 16 SYNCHRONOUS DRAM, 5.5 ns, PBGA60 |

| WE128K8200CQ | 128K X 8 EEPROM 5V MODULE, 200 ns, CDIP32 |

| WED9LC6816V1512BI | SPECIALTY MEMORY CIRCUIT, PBGA153 |

| WS128K32-35G2TMEA | 128K X 32 MULTI DEVICE SRAM MODULE, 35 ns, CQFP68 |

| WS128K32-55G2TIE | 128K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G6IB-25 | 功能描述:IC DDR2-800 SDRAM 256MB 84-WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.173",4.40mm 宽) 供应商设备封装:8-MFP 包装:带卷 (TR) |

| W9725G6JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:4M ? 4 BANKS ? 16 BIT DDR2 SDRAM |

| W9725G6JB-25 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin WBGA 制造商:Winbond Electronics 功能描述:512MB DDRII |

| W9725G6JB25I | 功能描述:IC DDR2 SDRAM 256MBIT 84WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

| W9725G6KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

发布紧急采购,3分钟左右您将得到回复。