- 您现在的位置:买卖IC网 > PDF目录69541 > W9725G6IB-18 (WINBOND ELECTRONICS CORP) 16M X 16 DDR DRAM, 0.35 ns, PBGA84 PDF资料下载

参数资料

| 型号: | W9725G6IB-18 |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | 16M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| 封装: | 8 X 12.50 MM, ROHS COMPLIANT, WBGA-84 |

| 文件页数: | 8/69页 |

| 文件大小: | 1644K |

| 代理商: | W9725G6IB-18 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

PRELIMINARY W9725G6IB

Publication Release Date:Nov. 14, 2008

- 16 -

Revision P04

7.2.3.1. Extended Mode Register for OCD Impedance Adjustment

OCD impedance adjustment can be done using the following EMRS mode. In drive mode all outputs

are driven out by DDR2 SDRAM. In Drive (1) mode, all DQ, DQS signals are driven HIGH and all

DQS signals are driven LOW. In Drive (0) mode, all DQ, DQS signals are driven LOW and all DQS

signals are driven HIGH. In adjust mode, BL = 4 of operation code data must be used. In case of OCD

calibration default, output driver characteristics have a nominal impedance value of 18 Ohms during

nominal temperature and voltage conditions. OCD applies only to normal full strength output drive

setting defined by EMR (1) and if reduced strength is set, OCD default driver characteristics are not

applicable. When OCD calibration adjust mode is used, OCD default output driver characteristics are

not applicable. After OCD calibration is completed or driver strength is set to default, subsequent

EMRS commands not intended to adjust OCD characteristics must specify A[9:7] as ’000’ in order to

maintain the default or calibrated value.

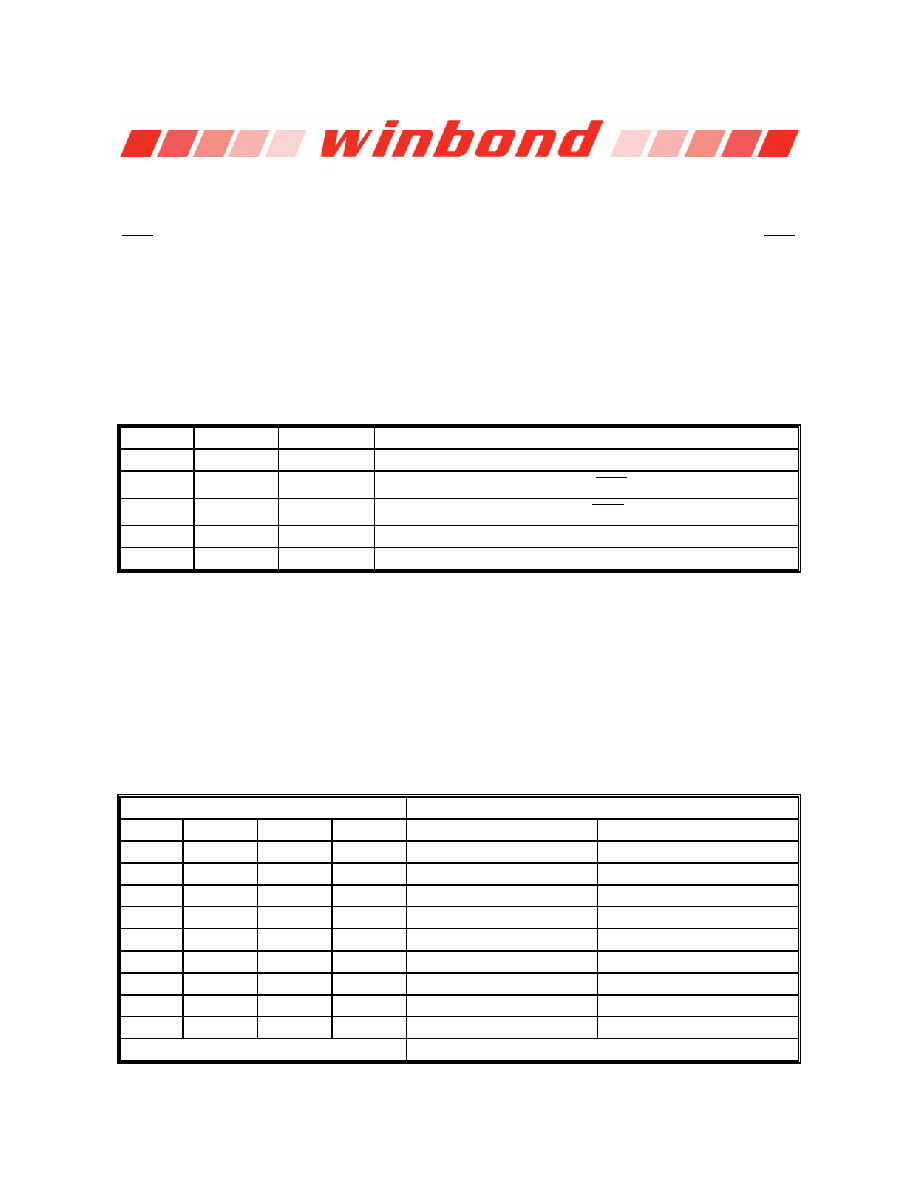

Table 1

—

—OCD Drive Mode Program

A9

A8

A7

Operation

0

OCD calibration mode exit

0

1

Drive (1) DQ, DQS HIGH and

DQS LOW

0

1

0

Drive (0) DQ, DQS LOW and

DQS HIGH

1

0

Adjust mode

1

OCD calibration default

7.2.3.2. OCD Impedance Adjust

To adjust output driver impedance, controllers must issue the ADJUST EMRS command along with a

4 bit burst code to DDR2 SDRAM as in table 2. For this operation, Burst Length has to be set to BL =

4 via MRS command before activating OCD and controllers must drive the burst code to all DQs at the

same time. DT0 in table 2 means all DQ bits at bit time 0, DT1 at bit time 1, and so forth. The driver

output impedance is adjusted for all DDR2 SDRAM DQs simultaneously and after OCD calibration, all

DQs and DQS’s of a given DDR2 SDRAM will be adjusted to the same driver strength setting. The

maximum step count for adjustment is 16 and when the limit is reached, further increment or

decrement code has no effect. The default setting may be any step within the 16 step range. When

Adjust mode command is issued, AL from previously set value must be applied.

Table 2

—

—OCD Adjust Mode Program

4 bit burst code inputs to all DQs

Operation

DT0

DT1

DT2

DT3

Pull-up driver strength

Pull-down driver strength

0

NOP (No operation)

0

1

Increase by 1 step

NOP

0

1

0

Decrease by 1 step

NOP

0

1

0

NOP

Increase by 1 step

1

0

NOP

Decrease by 1 step

0

1

0

1

Increase by 1 step

0

1

0

Decrease by 1 step

Increase by 1 step

1

0

1

Increase by 1 step

Decrease by 1 step

1

0

1

0

Decrease by 1 step

Other Combinations

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| W9864G6EB-7 | 4M X 16 SYNCHRONOUS DRAM, 5.5 ns, PBGA60 |

| WE128K8200CQ | 128K X 8 EEPROM 5V MODULE, 200 ns, CDIP32 |

| WED9LC6816V1512BI | SPECIALTY MEMORY CIRCUIT, PBGA153 |

| WS128K32-35G2TMEA | 128K X 32 MULTI DEVICE SRAM MODULE, 35 ns, CQFP68 |

| WS128K32-55G2TIE | 128K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G6IB-25 | 功能描述:IC DDR2-800 SDRAM 256MB 84-WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.173",4.40mm 宽) 供应商设备封装:8-MFP 包装:带卷 (TR) |

| W9725G6JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:4M ? 4 BANKS ? 16 BIT DDR2 SDRAM |

| W9725G6JB-25 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin WBGA 制造商:Winbond Electronics 功能描述:512MB DDRII |

| W9725G6JB25I | 功能描述:IC DDR2 SDRAM 256MBIT 84WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:150 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (2 x 256 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.5 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-DFN(2x3) 包装:管件 产品目录页面:1445 (CN2011-ZH PDF) |

| W9725G6KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

发布紧急采购,3分钟左右您将得到回复。