- 您现在的位置:买卖IC网 > PDF目录224693 > PC87393F-VJG (NATIONAL SEMICONDUCTOR CORP) 100-Pin LPC SuperI/O Devices for Portable Applications PDF资料下载

参数资料

| 型号: | PC87393F-VJG |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 外设及接口 |

| 英文描述: | 100-Pin LPC SuperI/O Devices for Portable Applications |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 101/148页 |

| 文件大小: | 1733K |

| 代理商: | PC87393F-VJG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页当前第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页

2.0 Device Architecture and Configuration (Continued)

56

www.national.com

2.15 GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION

This section applies to the PC87392, PC87393 and PC87393F only.

2.15.1

General Description

The GPIO functional block includes 32 pins, arranged in four 8-bit ports (ports 0, 1, 2 and 3). All pins in ports 0 and 1 are

I/O, and have full event detection capability, enabling them to trigger the assertion of IRQ and SMI signals. Pins in ports 2

and 3 are I/O, but none of them has event detection capability. The twelve runtime registers associated with the four ports

are arranged in the GPIO address space as shown in Table 23. The GPIO base address is 16-byte aligned. Address bits 3-

0 are used to indicate the register offset.

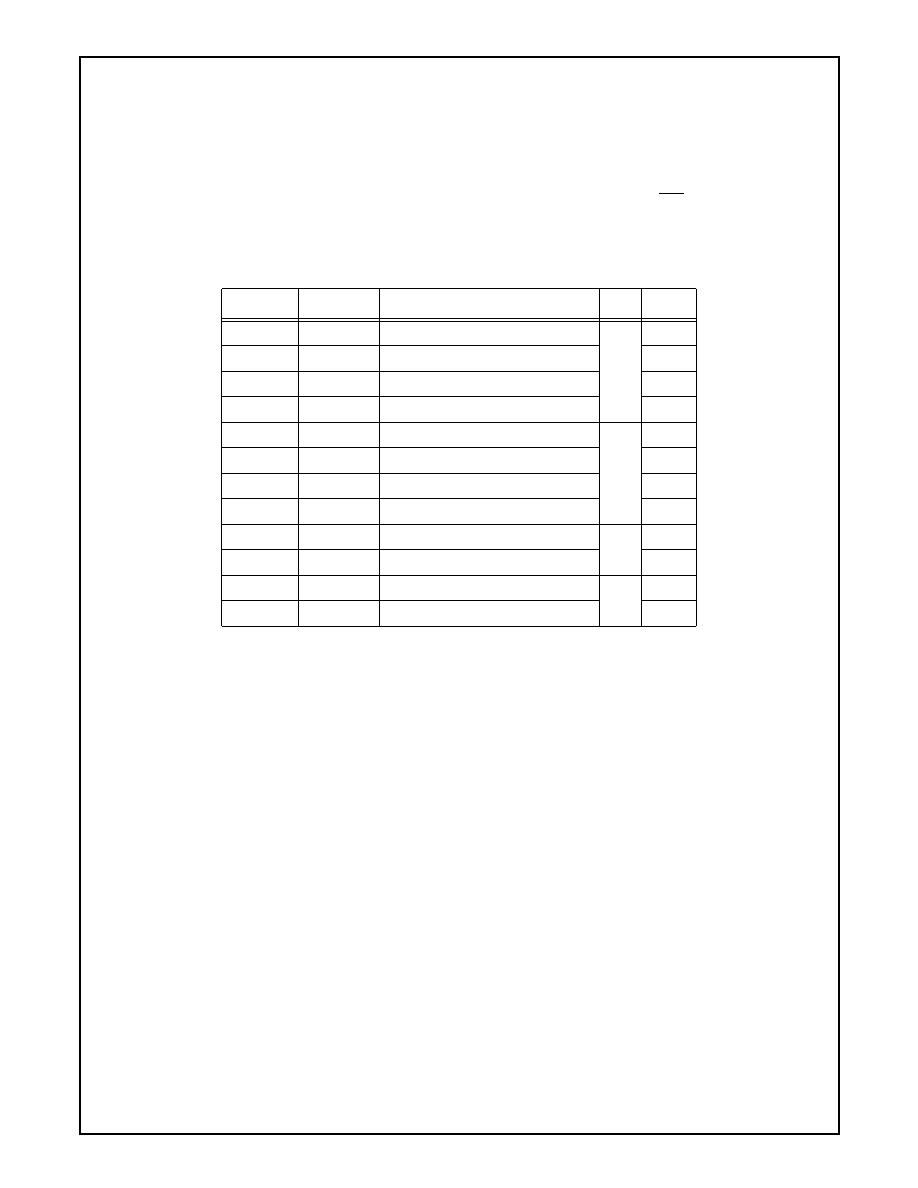

Table 23. Runtime Registers in GPIO Address Space

2.15.2

Implementation

The standard GPIO port with event detection capability (such as ports 0 and 1) has four runtime registers. Each pin is asso-

ciated with a GPIO Pin Configuration register that includes seven configuration bits. Ports 2 and 3 are non-standard ports

that do not support event detection, and therefore differ from the generic model as follows:

q

They each have two runtime registers for basic functionality: GPDO2/3 and GPDI2/3. Event detection registers

GPEVEN2/3 and GPEVST2/3 are not available.

q

Only bits 3-0 are implemented in the GPIO Pin Conguration registers of ports 2 and 3. Bits 6-4, associated with the

event detection functionality, are reserved.

Offset

Mnemonic

Register Name

Port

Type

00h

GPDO0

GPIO Data Out 0

0

R/W

01h

GPDI0

GPIO Data In 0

RO

02h

GPEVEN0 GPIO Event Enable 0

R/W

03h

GPEVST0 GPIO Event Status 0

R/W1C

04h

GPDO1

GPIO Data Out 1

1

R/W

05h

GPDI1

GPIO Data In 1

RO

06h

GPEVEN1 GPIO Event Enable 1

R/W

07h

GPEVST1 GPIO Event Status 1

R/W1C

08h

GPDO2

Data Out 2

2

R/W

09h

GPDI2

Data In 2

RO

0Ah

GPDO3

Data Out 3

3

R/W

0Bh

GPDI3

Data In 3

RO

相关PDF资料 |

PDF描述 |

|---|---|

| PC906N | 896 MHz - 940 MHz YAGI ANTENNA, 10.65 dBi GAIN, 65 deg 3dB BEAMWIDTH |

| PC926N | 928 MHz - 960 MHz YAGI ANTENNA, 10.65 dBi GAIN, 65 deg 3dB BEAMWIDTH |

| PCA.1D.694.CNAD42Z | CABLE TERMINATED, FEMALE, RF CONNECTOR, SOCKET |

| PCA.1D.694.CNAD42 | CABLE TERMINATED, FEMALE, RF CONNECTOR, SOCKET |

| PCA.1D.694.CNAD52Z | CABLE TERMINATED, FEMALE, RF CONNECTOR, SOCKET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PC87393VJG | 制造商:Texas Instruments 功能描述: 制造商:Texas Instruments 功能描述:IC, SUPER I/O DEVICE, TQFP-100, Logic Device Type:Buffer, Supply Voltage Min:3V, |

| PC87393-VJG | 制造商:NSC 制造商全称:National Semiconductor 功能描述:100-Pin LPC SuperI/O Devices for Portable Applications |

| PC87410 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PC87410 PCI-IDE Interface Controller |

| PC87410VLK | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| PC87413 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:LPC ServerI/O for Servers and Workstations |

发布紧急采购,3分钟左右您将得到回复。