- 您现在的位置:买卖IC网 > PDF目录69323 > RN80532KC0412M (INTEL CORP) 2000 MHz, MICROPROCESSOR, CPGA603 PDF资料下载

参数资料

| 型号: | RN80532KC0412M |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2000 MHz, MICROPROCESSOR, CPGA603 |

| 封装: | Interposer, Micro, PGA-603 |

| 文件页数: | 62/132页 |

| 文件大小: | 2316K |

| 代理商: | RN80532KC0412M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页

Intel Xeon Processor MP with up to 2MB L3 Cache

2-21

Electrical Specifications

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies and cache sizes.

2. Not 100% tested. Specified by design characterization.

3. All AC timings for the TAP signals are referenced to the TCK signal at 0.5 * Vcc at the processor pins. All TAP

signal timings (TMS, TDI, etc) are referenced at the 0.5 * Vcc processor pins.

4. Rise and fall times are measured from the 20% to 80% points of the signal swing.

5. Referenced to the rising edge of TCK.

6. Referenced to the falling edge of TCK.

7. Specification for a minimum swing defined between TAP 20% to 80%. This assumes a minimum edge rate of

0.5 V/ns

8. TRST# must be held asserted for 2 TCK periods to be guaranteed that it is recognized by the processor.

9. It is recommended that TMS be asserted while TRST# is being deasserted.

.

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies and cache sizes.

2. These parameters are based on design characterization and are not tested.

3. All AC timings for the SMBus signals are referenced at VIL_MAX or VIH_MIN and measured at the processor

pins. Refer to Figure 16.

4. Minimum time allowed between request cycles.

5. Rise time is measured from (VIL_MAX - 0.15 V) to (VIH_MIN + 0.15 V). Fall time is measured from (0.9 *

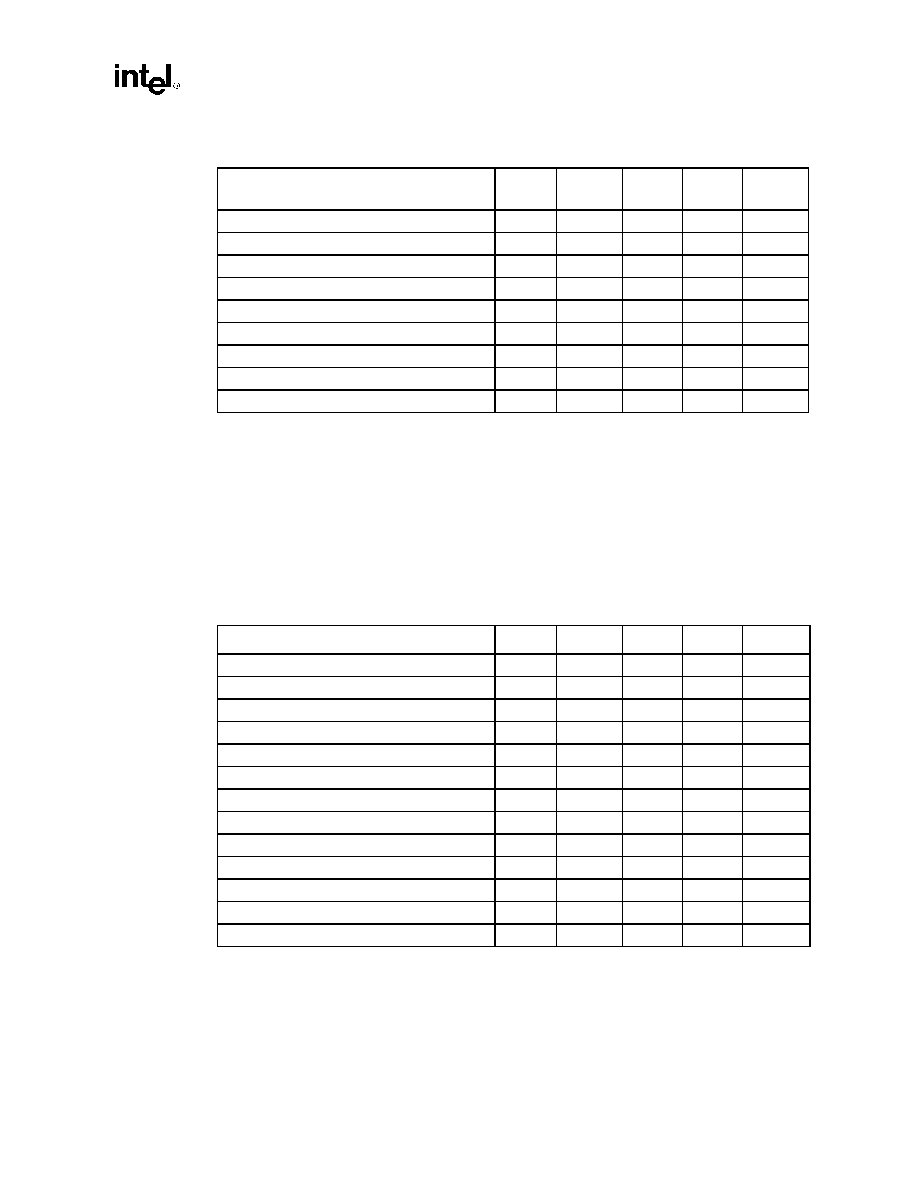

Table 20. TAP Signal Group AC Specifications

T# Parameter

Min

Max

Unit

Figure

Notes

1,2,3,9

T55: TCK Period

60.0

ns

T56: TCK Rise Time

9.5

ns

4

T57: TCK Fall Time

9.5

ns

4

T58: TMS, TDI Rise Time

8.5

ns

4

T59: TMS, TDI Fall Time

8.5

ns

4

T61: TDI, TMS Setup Time

0

ns

5, 7

T62: TDI, TMS Hold Time

3.0

ns

5,7

T63: TDO Clock to Output Delay

0.5

3.5

ns

6

T64: TRST# Assert Time

2.0

TTCK

8

Table 21. SMBus Signal Group AC Specifications

T# Parameter

Min

Max

Unit

Figure

Notes1,2,3

T70: SM_CLK Frequency

10

100

KHz

T71: SM_CLK Period

10

100

s

T72: SM_CLK High Time

4.0

N/A

s

T73: SM_CLK Low Time

4.7

N/A

s

T74: SMBus Rise Time

0.02

1.0

s

5

T75: SMBus Fall Time

0.02

0.3

s

5

T76: SMBus Output Valid Delay

0.1

4.5

s

T77: SMBus Input Setup Time

250

N/A

ns

T78: SMBus Input Hold Time

300

N/A

ns

T79: Bus Free Time

4.7

N/A

s

4, 6

T80: Hold Time after Repeated Start Condition

4.0

N/A

s

T81: Repeated Start Condition Setup Time

4.7

N/A

s

T82: Stop Condition Setup Time

4.0

N/A

s

相关PDF资料 |

PDF描述 |

|---|---|

| RN80532KC041512 | 32-BIT, 2000 MHz, MICROPROCESSOR, CPGA603 |

| RP0352 | GRAPHICS PROCESSOR, PQFP80 |

| RP65C02G-06 | 8-BIT, 6 MHz, MICROPROCESSOR, PDIP40 |

| RPIXP2800BC | 32-BIT, 650 MHz, RISC PROCESSOR, PBGA1356 |

| RPIXP2850BB | 32-BIT, 1400 MHz, RISC PROCESSOR, PBGA1356 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RN80532KC041512 | 制造商:Intel 功能描述:TRAY XEON 2.0GHZ 400MZH FSB - Trays 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RN80532KC041512 SL5Z9 | 制造商:Intel 功能描述:MPU XEON 0.13UM 2GHZ 603-PIN UFCBGA - Trays |

| RN80532KC041512 SL6EM | 制造商:Intel 功能描述:MPU XEON 0.13UM 2GHZ 603-PIN UFCBGA - Trays |

| RN80532KC041512S L5Z9 | 制造商:Intel 功能描述:MPU Xeon? Processor 0.13um 2GHz 603-Pin uFCBGA |

| RN80532KC041512S L6W6 | 制造商:Intel 功能描述:MPU Xeon? Processor 0.13um 2GHz 603-Pin uFCBGA |

发布紧急采购,3分钟左右您将得到回复。