- 您现在的位置:买卖IC网 > PDF目录68559 > W9725G8JB-25I (WINBOND ELECTRONICS CORP) DDR DRAM, PBGA84 PDF资料下载

参数资料

| 型号: | W9725G8JB-25I |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM, PBGA84 |

| 封装: | 8 X 12.50 MM, ROHS COMPLIANT, WBGA-84 |

| 文件页数: | 11/86页 |

| 文件大小: | 1462K |

| 代理商: | W9725G8JB-25I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

W9725G8JB

Publication Release Date: Oct. 12, 2010

- 19 -

Revision A01

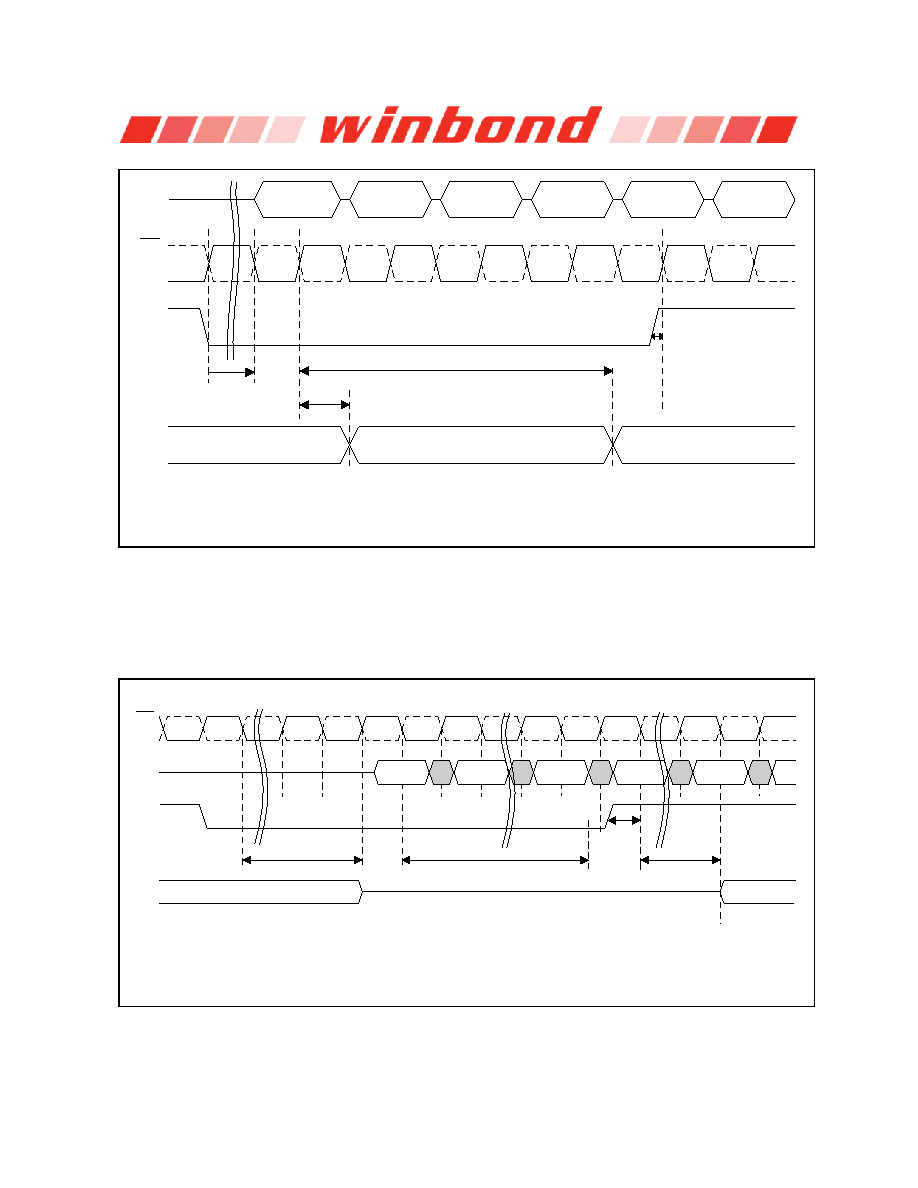

CMD

CLK

ODT

Rtt

Updating

New setting

tIS

tMOD,min

tMOD,max

tAOFD

EMRS

NOP

Old setting

1) EMRS command directed to EMR(1), which updates the information in EMR(1)[A6,A2], i.e. Rtt (Nominal).

2) "setting" in this diagram is the Register and I/O setting, not what is measured from outside.

Figure 10

– ODT update delay timing - tMOD

However, to prevent any impedance glitch on the channel, the following conditions must be met.

tAOFD must be met before issuing the EMRS command.

ODT must remain LOW for the entire duration of tMOD window, until tMOD,max is met.

Now the ODT is ready for normal operation with the new setting, and the ODT signal may be raised

again to turned on the ODT. Following timing diagram shows the proper Rtt update procedure.

CLK

CMD

ODT

Rtt

Old setting

New setting

tAOND

tIS

tMOD,max

tAOFD

EMRS

NOP

1) EMRS command directed to EMR(1), which updates the information in EMR(1)[A6,A2], i.e. Rtt (Nominal).

2) "setting" in this diagram is what is measured from outside.

Figure 11

– ODT update delay timing - tMOD, as measured from outside

相关PDF资料 |

PDF描述 |

|---|---|

| W972GG8JB-25I | 256M X 8 DDR DRAM, 0.4 ns, PBGA60 |

| W972GG8JB-18 | 256M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| W9751G6JB-18 | 32M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| W981204AH-8H | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| W981216BH75L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G8JB25ITR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8, IND TEMP |

| W9725G8JB25TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

| W9725G8KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

发布紧急采购,3分钟左右您将得到回复。