- 您现在的位置:买卖IC网 > PDF目录68559 > W9725G8JB-25I (WINBOND ELECTRONICS CORP) DDR DRAM, PBGA84 PDF资料下载

参数资料

| 型号: | W9725G8JB-25I |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM, PBGA84 |

| 封装: | 8 X 12.50 MM, ROHS COMPLIANT, WBGA-84 |

| 文件页数: | 15/86页 |

| 文件大小: | 1462K |

| 代理商: | W9725G8JB-25I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

W9725G8JB

Publication Release Date: Oct. 12, 2010

- 22 -

Revision A01

7.3.8

Self Refresh Exit Command

(CKE = "H", CS = "H" or CKE = "H", CS = "L", RAS = "H", CAS = "H", WE = "H", BA0, BA1,

A0 to A12 = Don

t Care)

The procedure for exiting Self Refresh requires a sequence of commands. First, the clock must be

stable prior to CKE going back HIGH. Once Self Refresh Exit is registered, a delay of at least tXSNR

must be satisfied before a valid command can be issued to the device to allow for any internal refresh

in progress. CKE must remain HIGH for the entire Self Refresh exit period tXSRD for proper operation

except for self refresh re-entry.

Upon exit from Self Refresh, the DDR2 SDRAM can be put back into Self Refresh mode after waiting

at least tXSNR period and issuing one refresh command (refresh period of tRFC). NOP or Deselect

commands must be registered on each positive clock edge during the Self Refresh exit interval tXSNR.

ODT should be turned off during tXSRD.

The use of Self Refresh mode introduces the possibility that an internally timed refresh event can be

missed when CKE is raised for exit from Self Refresh mode. Upon exit from Self Refresh, the DDR2

SDRAM requires a minimum of one extra auto refresh command before it is put back into Self Refresh

mode.

7.3.9

Refresh Command

( CS = "L", RAS = "L", CAS = "L", WE = "H", CKE = "H", BA0, BA1, A0 to A12 = Dont Care)

Refresh is used during normal operation of the DDR2 SDRAM. This command is non persistent, so it

must be issued each time a refresh is required.

The refresh addressing is generated by the internal refresh controller. This makes the address

bits

”Dont Care” during an Auto Refresh command. The DDR2 SDRAM requires Auto Refresh cycles

at an average periodic interval of

tREFI (max.).

When the refresh cycle has completed, all banks of the DDR2 SDRAM will be in the precharged (idle)

state. A delay between the auto refresh command (REF) and the next activate command or

subsequent auto refresh command must be greater than or equal to the auto refresh cycle time (tRFC).

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the

absolute refresh interval is provided. A maximum of eight Refresh commands can be posted to any

given DDR2 SDRAM, meaning that the maximum absolute interval between any Refresh command

and the next Refresh command is 9 x tREFI.

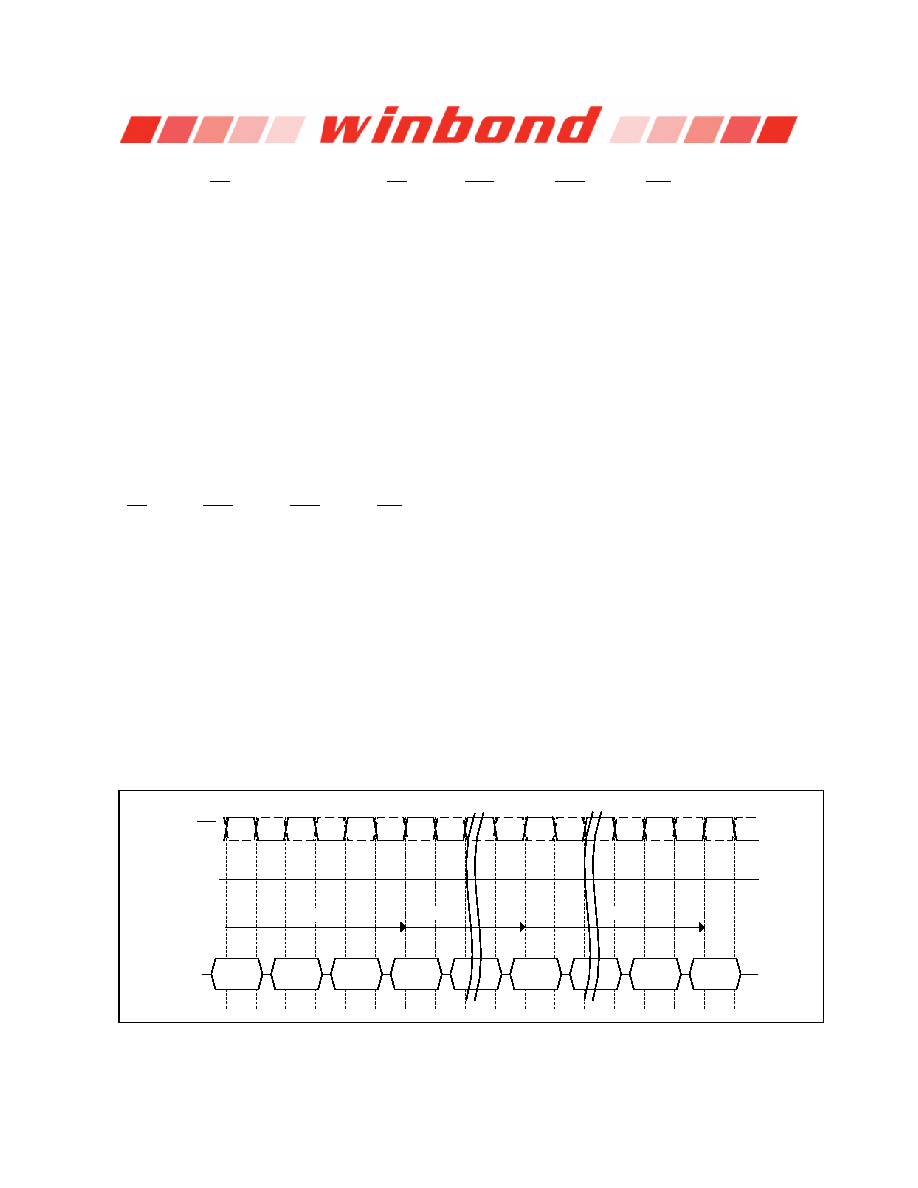

T0

T1

T2

T3

CLK/CLK

CKE

CMD

≥ tRP

≥ tRFC

NOP

ANY

REF

Precharge

"HIGH"

Tm

Tn

Tn + 1

Figure 13

– Refresh command

相关PDF资料 |

PDF描述 |

|---|---|

| W972GG8JB-25I | 256M X 8 DDR DRAM, 0.4 ns, PBGA60 |

| W972GG8JB-18 | 256M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| W9751G6JB-18 | 32M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| W981204AH-8H | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| W981216BH75L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G8JB25ITR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8, IND TEMP |

| W9725G8JB25TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

| W9725G8KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

发布紧急采购,3分钟左右您将得到回复。