- 您现在的位置:买卖IC网 > PDF目录68559 > W9725G8JB-25I (WINBOND ELECTRONICS CORP) DDR DRAM, PBGA84 PDF资料下载

参数资料

| 型号: | W9725G8JB-25I |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | DDR DRAM, PBGA84 |

| 封装: | 8 X 12.50 MM, ROHS COMPLIANT, WBGA-84 |

| 文件页数: | 47/86页 |

| 文件大小: | 1462K |

| 代理商: | W9725G8JB-25I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

W9725G8JB

Publication Release Date: Oct. 12, 2010

- 51 -

Revision A01

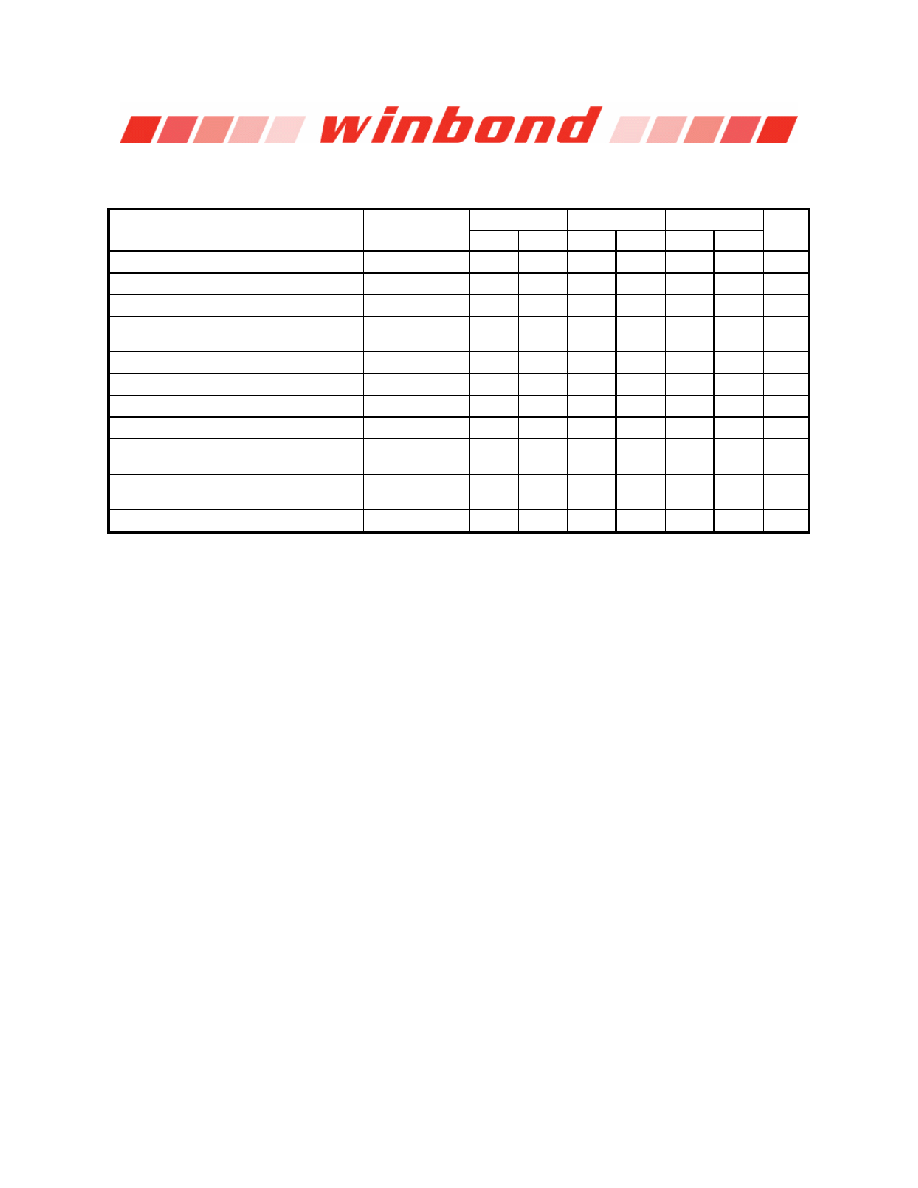

30. Input clock jitter spec parameter. These parameters and the ones in the table below are referred to as 'input clock jitter spec

parameters'. The jitter specified is a random jitter meeting a Gaussian distribution.

Input clock-Jitter specifications parameters for DDR2-667, DDR2-800 and DDR2-1066

PARAMETER

SYMBOL

DDR2-667

DDR2-800

DDR2-1066

UNIT

MIN.

MAX.

MIN.

MAX.

MIN.

MAX.

Clock period jitter

tJIT(per)

-125

125

-100

100

-90

90

pS

Clock period jitter during DLL locking period

tJIT(per,lck)

-100

100

-80

80

-80

80

pS

Cycle to cycle clock period

tJIT(cc)

-250

250

-200

200

-180

180

pS

Cycle to cycle clock period jitter during DLL

locking period

tJIT(cc,lck)

-200

200

-160

160

-160

160

pS

Cumulative error across 2 cycles

tERR(2per)

-175

175

-150

150

-132

132

pS

Cumulative error across 3 cycles

tERR(3per)

-225

225

-175

175

-157

157

pS

Cumulative error across 4 cycles

tERR(4per)

-250

250

-200

200

-175

175

pS

Cumulative error across 5 cycles

tERR(5per)

-250

250

-200

200

-188

188

pS

Cumulative error across n cycles,

n = 6 ... 10, inclusive

tERR(6-10per)

-350

350

-300

300

-250

250

pS

Cumulative error across n cycles,

n = 11 ... 50, inclusive

tERR(11-50per)

-450

450

-450

450

-425

425

pS

Duty cycle jitter

tJIT(duty)

-125

125

-100

100

-75

75

pS

Definitions:

-

tCK(avg)

tCK(avg) is calculated as the average clock period across any consecutive 200 cycle window.

tCK(avg) =

N

j

tCK

1

/ N

where

N = 200

-

tCH(avg) and tCL(avg)

tCH(avg) is defined as the average HIGH pulse width, as calculated across any consecutive 200 HIGH pulses.

tCH(avg) =

N

j

tCH

1

/ (N × tCK(avg))

where

N = 200

tCL(avg) is defined as the average LOW pulse width, as calculated across any consecutive 200 LOW pulses.

tCL(avg) =

N

j

tCL

1

/ (N × tCK(avg))

where

N = 200

相关PDF资料 |

PDF描述 |

|---|---|

| W972GG8JB-25I | 256M X 8 DDR DRAM, 0.4 ns, PBGA60 |

| W972GG8JB-18 | 256M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| W9751G6JB-18 | 32M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| W981204AH-8H | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| W981216BH75L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9725G8JB25ITR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8, IND TEMP |

| W9725G8JB25TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

| W9725G8KB-18 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 | 制造商:Winbond Electronics 功能描述:IC MEMORY 制造商:Winbond Electronics Corp 功能描述:IC MEMORY |

| W9725G8KB-25 TR | 制造商:Winbond Electronics Corp 功能描述:256M DDR2-800, X8 |

发布紧急采购,3分钟左右您将得到回复。