- 您现在的位置:买卖IC网 > PDF目录385639 > MT48V4M32LFFC (Micron Technology, Inc.) SYNCHRONOUS DRAM PDF资料下载

参数资料

| 型号: | MT48V4M32LFFC |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | SYNCHRONOUS DRAM |

| 中文描述: | 同步DRAM |

| 文件页数: | 30/61页 |

| 文件大小: | 1400K |

| 代理商: | MT48V4M32LFFC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

30

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2002, Micron Technology, Inc.

128Mb: x16, x32

MOBILE SDRAM

ADVANCE

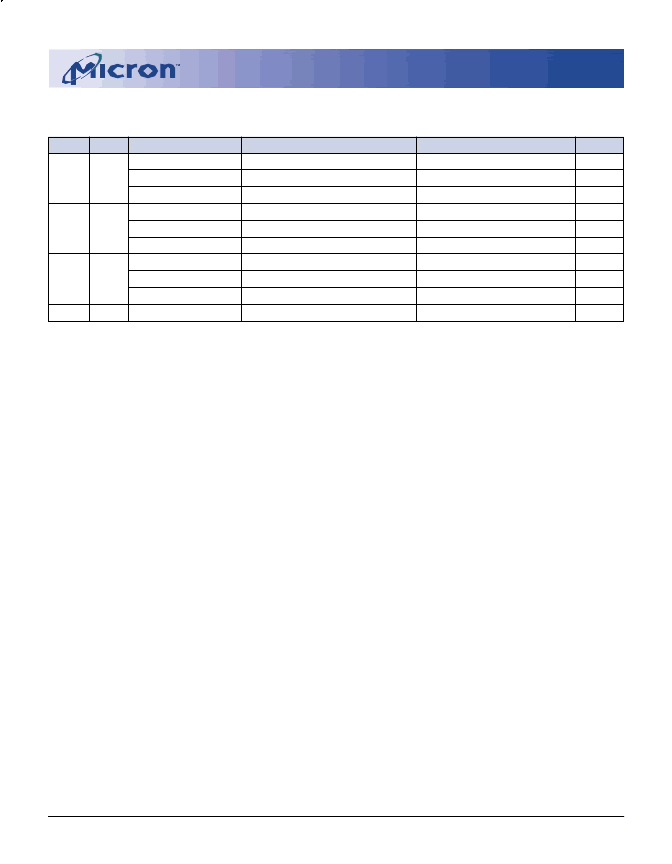

TRUTH TABLE 2 – CKE

(Notes: 1-4)

CKE

n-1

CKE

n

L

CURRENT STATE

Power-Down

Self Refresh

Clock Suspend

Power-Down

Self Refresh

Clock Suspend

All Banks Idle

All Banks Idle

Reading or Writing

COMMAND

n

X

X

X

ACTION

n

Maintain Power-Down

Maintain Self Refresh

Maintain Clock Suspend

Exit Power-Down

Exit Self Refresh

Exit Clock Suspend

Power-Down Entry

Self Refresh Entry

Clock Suspend Entry

NOTES

L

L

H

COMMAND INHIBIT or NOP

COMMAND INHIBIT or NOP

X

COMMAND INHIBIT or NOP

AUTO REFRESH

VALID

See Truth Table 3

5

6

7

H

L

H

H

NOTE:

1. CKE

is the logic state of CKE at clock edge

n

; CKE

was the state of CKE at the previous clock edge.

2. Current state is the state of the SDRAM immediately prior to clock edge

n

.

3. COMMAND

is the command registered at clock edge

n

, and ACTION

n

is a result of COMMAND

n

.

4. All states and sequences not shown are illegal or reserved.

5. Exiting power-down at clock edge

n

will put the device in the all banks idle state in time for clock edge

n + 1

(provided that

t

CKS is met).

6. Exiting self refresh at clock edge

n

will put the device in the all banks idle state once

t

XSR is met. COMMAND INHIBIT

or NOP commands should be issued on any clock edges occurring during the

t

XSR period. A minimum of two NOP

commands must be provided during

t

XSR period.

7. After exiting clock suspend at clock edge

n

, the device will resume operation and recognize the next command at

clock edge

n + 1

.

相关PDF资料 |

PDF描述 |

|---|---|

| MT49H16M16 | THERMISTOR PTC 100OHM 110DEG RAD |

| MT49H16M16FM | REDUCED LATENCY DRAM RLDRAM |

| MT49H8M32 | THERMISTOR PTC 100OHM 120DEG RAD |

| MT49H8M32FM | REDUCED LATENCY DRAM RLDRAM |

| MT4C1M16E5DJ-6 | EDO DRAM |

相关代理商/技术参数 |

参数描述 |

|---|

发布紧急采购,3分钟左右您将得到回复。