- 您现在的位置:买卖IC网 > PDF目录365968 > TSB12LV26PZ (Texas Instruments, Inc.) OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER PDF资料下载

参数资料

| 型号: | TSB12LV26PZ |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| 中文描述: | OHCI的山猫基于PCI的1394主控制器 |

| 文件页数: | 101/106页 |

| 文件大小: | 605K |

| 代理商: | TSB12LV26PZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页当前第101页第102页第103页第104页第105页第106页

8

–

8

00

00

10

00

01

XX

dn

d0

SPD

(a)

(e)

(d)

(b)

(c)

FF (

“

data

–

on

”

)

D0

–

D7

CTL0, CTL1

SYSCLK

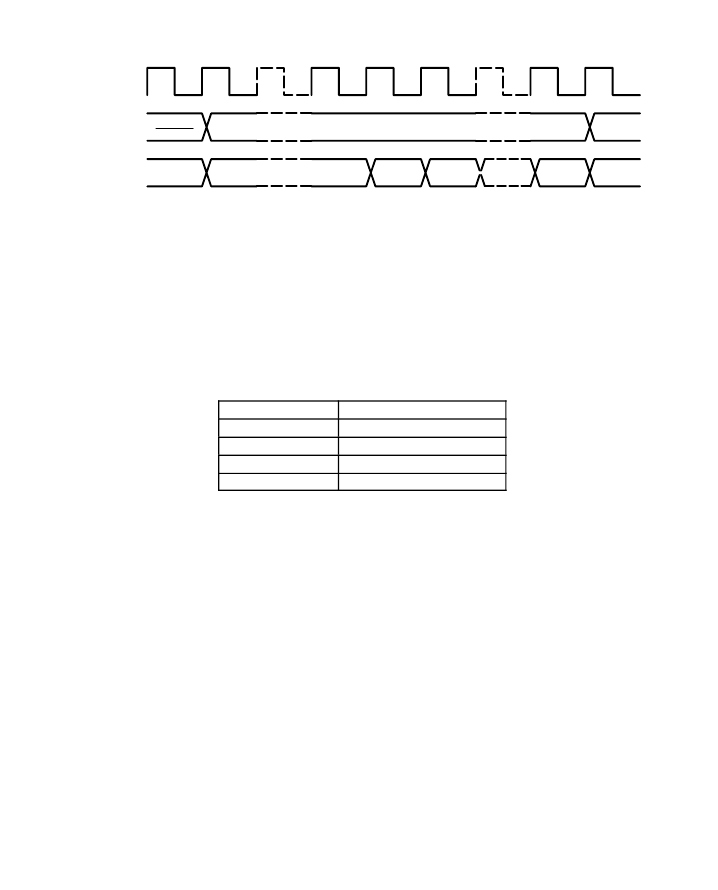

Figure 8

–

5. Null Packet Reception Timing

The sequence of events for a null packet reception is as follows:

Receive operation initiated. The Phy indicates a receive operation by asserting receive on the

CTL lines. Normally, the interface is idle when receive is asserted. However, the receive operation

may interrupt a status transfer operation that is in progress so that the CTL lines may change from

status to receive without an intervening idle.

Data-on indication. The Phy asserts the data-on indication code on the D lines for one or more

cycles.

Receive operation terminated. The Phy terminates the receive operation by asserting idle on the

CTL lines. The Phy asserts at least one cycle of idle following a receive operation.

Table 8

–

11. Receive Speed Codes

D0

–

D7

DATA RATE

00XX XXXX

S100

0100 XXXX

S200

0101 0000

S400

1YYY YYYY

Data-on indication

NOTE: X = Output as 0 by Phy, ignored by TSB12LV32.

Y = Output as 1 by Phy, ignored by TSB12LV3

8.5

When the TSB12LV32 issues a bus request through the LREQ terminal, the Phy arbitrates to gain control

of the bus. If the Phy wins arbitration for the serial bus, the Phy-LLC interface bus is granted to the

TSB12LV32 by asserting the grant state (

’

b11) on the CTL terminals for one SYSCLK cycle, followed by idle

for one clock cycle. The TSB12LV32 then takes control of the bus by asserting either idle (

’

b00), hold (

’

b01)

or transmit (

’

b10) on the CTL terminals. Unless the TSB12LV32 is immediately releasing the interface, the

TSB12LV32 may assert the idle state for at most one clock before it must assert either hold or transmit on

the CTL terminals. The hold state is used by the TSB12LV32 to retain control of the bus while it prepares

data for transmission. The TSB12LV32 may assert hold for zero or more clock cycles (i.e., the TSB12LV32

need not assert hold before transmit). The Phy asserts data-prefix on the serial bus during this time.

Transmit Operation

When the TSB12LV32 is ready to send data, the TSB12LV32 asserts transmit on the CTL terminals as well

as sending the first bits of packet data on the D lines. The transmit state is held on the CTL terminals until

the last bits of data have been sent. The TSB12LV32 then asserts either hold or idle on the CTL terminals

for one clock cycle, and then asserts idle for one additional cycle before releasing the interface bus and

placing its CTL and D terminals in high impedance. The Phy then regains control of the interface bus.

The hold state asserted at the end of packet transmission indicates to the Phy that the TSB12LV32 requests

to send another packet (concatenated packet) without releasing the serial bus. The Phy responds to this

concatenation request by waiting the required minimum packet separation time and then asserting grant

as before. This function may be used to send a unified response after sending an acknowledge, or to send

相关PDF资料 |

PDF描述 |

|---|---|

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB12LV26PZT | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26PZTG4 | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based IEEE1394 Host Cntrlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26TPZEP | 功能描述:1394 接口集成电路 Mil Enh OHCI-Lynx IEEE 1394 Host Cntlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV31 | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB12LV31PZ | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 General-Purpose Link-Layer Controller |

发布紧急采购,3分钟左右您将得到回复。