- 您现在的位置:买卖IC网 > PDF目录365968 > TSB12LV26PZ (Texas Instruments, Inc.) OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER PDF资料下载

参数资料

| 型号: | TSB12LV26PZ |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| 中文描述: | OHCI的山猫基于PCI的1394主控制器 |

| 文件页数: | 87/106页 |

| 文件大小: | 605K |

| 代理商: | TSB12LV26PZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页当前第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

7

–

9

7.3

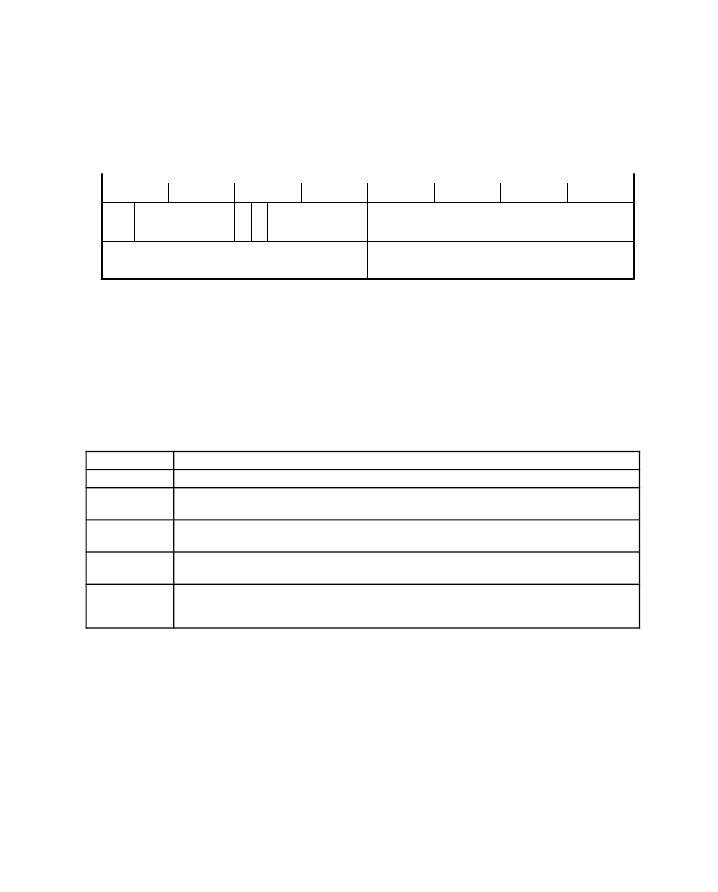

The format of the Phy configuration packet is shown in Figure 7-12 and is described in Table 7-8. The Phy

configuration packet transmit contains two quadlets, which are loaded into the ATF. The first quadlet is

written to address 50h. The second quadlet is written to address 58h. The 00E0h in the first quadlet (bits

16

–

31) tells the TSB12LV32 that this quadlet is the Phy configuration packet. The Eh is then replaced with

0h before the packet is transmitted to the Phy interface.

Phy Configuration

3

2

1

0

7

6

5

4

11

10

9

8

15

14

13

12

19

18

20 21

31

30

29

28

27

26

25

24

23

22

0

0

root_ID

T

R

gap_cnt

0

0

0

0

0

0

0

0

1

1

1

0

0

Logical inverse of first 16 bits of first quadlet

1

1

1

1

1

1

1

1

1

1

1

1

1

1

tcode =

’

E

’

0

0

0

17

16

1

1

Figure 7

–

11. Phy Configuration Packet Format

The Phy configuration packet can perform the following functions:

Set the gap count field of all nodes on the bus to a new value. The gap count, if set intelligently,

can optimize bus performance.

Force a particular node to be the bus root after the next bus reset.

It is not valid to transmit a Phy configuration packet with both the R bit and T bit set to zero. This would cause

the packet to be interpreted as an extended Phy packet.

Table 7

–

7. Phy Configuration Packet Functions

FIELD NAME

DESCRIPTION

00

The 00 field is the Phy configuration packet identifier.

root_ID

The root_ID field is the physical_ID of the node to have its force_root bit set (only meaningful when R

is set).

R

When R is set, the force-root bit of the node identified in root_ID is set and the force_root bit of all

other nodes are cleared. When R is cleared, root_ID is ignored.

T

When T is set, the PHY_CONFIGURATION.gap_count field of all the nodes is set to the value in the

gap_cnt field.

gap_cnt

The gap_cnt field contains the new value for PHY_CONFIGURATION.gap_count for all nodes. This

value goes into effect immediately upon receipt and remains valid after the next bus reset. After the

second reset, gap_cnt is set to 63h unless a new Phy configuration packet is received.

The format of a received Phy-configuration packet is shown in Figure 7

–

12 and is described in Table 7

–

8.

When PHY_PKT_ENA (bit 3 of the control register @08h) is set, all Phy packets will be received in the GRF.

One HDRERR interrupt will be generated for every Phy packet received.

相关PDF资料 |

PDF描述 |

|---|---|

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB12LV26PZT | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26PZTG4 | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based IEEE1394 Host Cntrlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26TPZEP | 功能描述:1394 接口集成电路 Mil Enh OHCI-Lynx IEEE 1394 Host Cntlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV31 | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB12LV31PZ | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 General-Purpose Link-Layer Controller |

发布紧急采购,3分钟左右您将得到回复。