- 您现在的位置:买卖IC网 > PDF目录365968 > TSB12LV26PZ (Texas Instruments, Inc.) OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER PDF资料下载

参数资料

| 型号: | TSB12LV26PZ |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| 中文描述: | OHCI的山猫基于PCI的1394主控制器 |

| 文件页数: | 54/106页 |

| 文件大小: | 605K |

| 代理商: | TSB12LV26PZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页当前第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

4

–

1

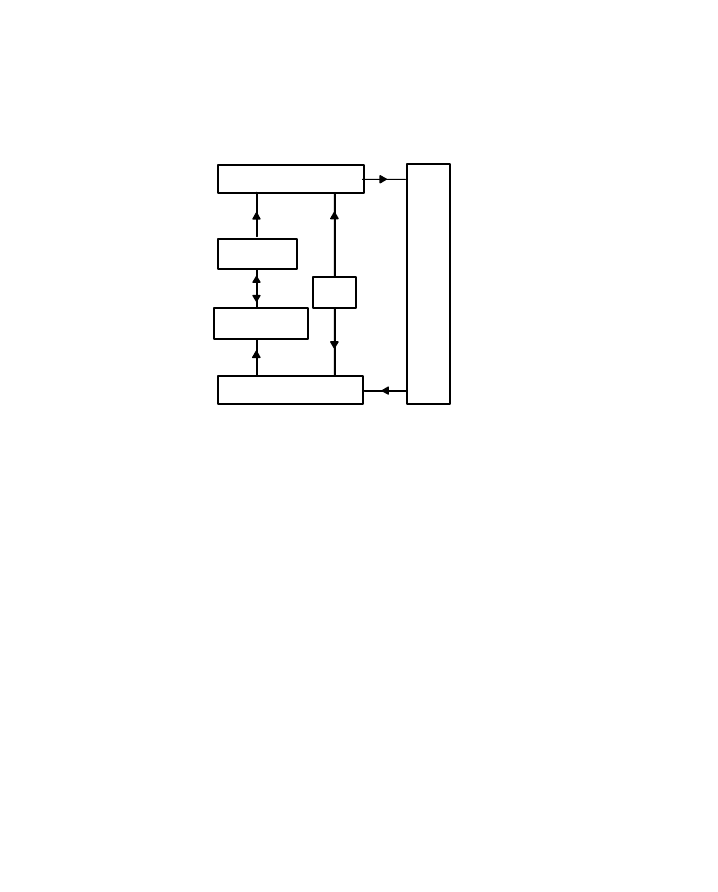

4 Link Core

This section describes the link core components and operations. Figure 4

–

1 shows the link core

components.

Transmitter

Cycle Timer

Cycle Monitor

CRC

Receiver

P

Figure 4

–

1. Link Core Components

4.1

The physical (Phy) interface provides Phy-level services to the transmitter and receiver. This includes

gaining access to the serial bus, sending packets, receiving packets, and sending and receiving

acknowledge packets. The Phy interface module also interfaces to the Phy chip and implements Texas

Instruments patent-pending bus-holder galvanic isolation.

4.2

Transmitter

The transmitter retrieves data from either the asynchronous transmit FIFO (ATF) or the data mover (DM)

port and creates correctly formatted serial-bus packets to be transmitted through the Phy interface. When

data is present at the ATF interface to the transmitter, the TSB12LV32 Phy interface arbitrates for the serial

bus and sends a packet. When data is present at the DM Port, the TSB12LV32 arbitrates for the serial bus

during the next isochronous cycle. The transmitter autonomously sends the cycle-start packets when the

chip is a cycle master.

4.3

Receiver

The receiver takes incoming data from the Phy interface and determines if the incoming data is addressed

to this node. When the incoming packet is addressed to this node, the CRC of the packet is checked. If the

header CRC is good, the header is confirmed in the general-receive FIFO (GRF). For block and isochronous

packets, the remainder of the packet is confirmed one quadlet at a time. The receiver places a status quadlet

in the GRF after the last quadlet of the packet is confirmed in the GRF. The status quadlet contains the error

code for the packet. In the case of asynchronous packets, the error code is the acknowledge code that is

sent (returned) for that packet. For isochronous and broadcast packets that do not need acknowledge

packets, the error code is the acknowledge code that would have been sent. This acknowledge code tells

the transaction layer whether or not the data CRC is good or bad. If the header CRC is bad, the header is

flushed and the rest of the packet is ignored. When a cycle-start packet is received, it is detected and the

cycle-start packet data is sent to the cycle timer. Cycle-start packets are not placed in the GRF like other

quadlet packets.

Physical Interface

相关PDF资料 |

PDF描述 |

|---|---|

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB12LV26PZT | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26PZTG4 | 功能描述:1394 接口集成电路 OHCI-Lynx PCI-Based IEEE1394 Host Cntrlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV26TPZEP | 功能描述:1394 接口集成电路 Mil Enh OHCI-Lynx IEEE 1394 Host Cntlr RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB12LV31 | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB12LV31PZ | 制造商:TI 制造商全称:Texas Instruments 功能描述:IEEE 1394-1995 General-Purpose Link-Layer Controller |

发布紧急采购,3分钟左右您将得到回复。