- 您现在的位置:买卖IC网 > PDF目录202173 > V59C1G01808QALF19E (PROMOS TECHNOLOGIES INC) 128M X 8 DDR DRAM, BGA68 PDF资料下载

参数资料

| 型号: | V59C1G01808QALF19E |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 128M X 8 DDR DRAM, BGA68 |

| 封装: | ROHS COMPLIANT, FBGA-68 |

| 文件页数: | 43/79页 |

| 文件大小: | 1028K |

| 代理商: | V59C1G01808QALF19E |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

48

V59C1G01(408/808/168)QA Rev. 1.3 June 2008

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QA

Refresh

SDRAMs require a refresh of all rows in any rolling 64 ms interval. Each refresh is generated in one of two

ways : by an explicit Auto-Refresh command, or by an internally timed event in Self-Refresh mode. Dividing

the number of device rows into the rolling 64 ms interval defined the average refresh interval tREFI, which is

a guideline to controlles for distributed refresh timing. For example, a 512Mbit DDR2 SDRAM has 8192 rows

resulting in a tREFI of 7,8 s.

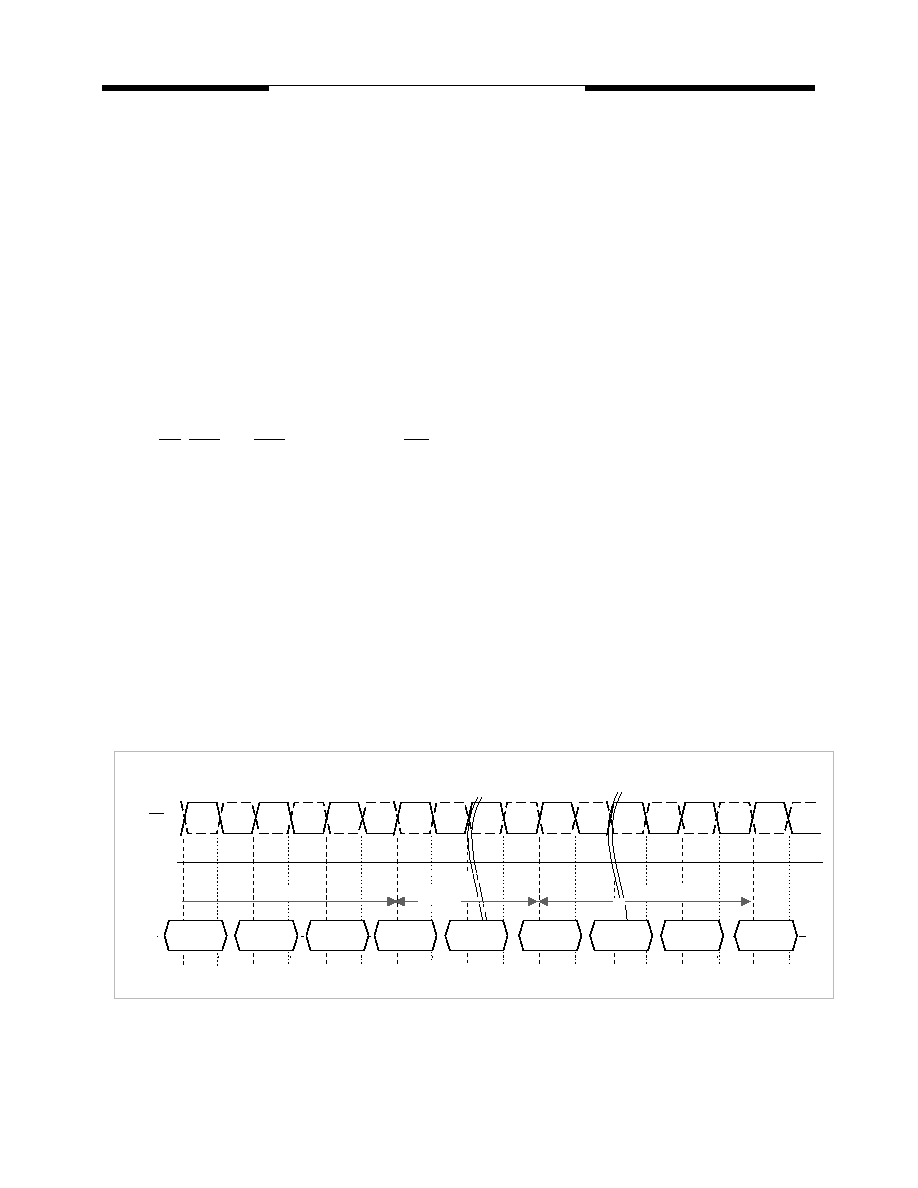

Auto-Refresh Command

Auto-Refresh is used during normal operation of the DDR2 SDRAMs. This command is nonpersistent, so it

must be issued each time a refresh is required. The refresh addressing is generated by the internal refresh

controller. This makes the address bits ”Don’t Care” during an Auto-Refresh command. The DDR2 SDRAM

requires Auto-Refresh cycles at an average periodic interval of tREFI (maximum).

When CS, RAS and CAS are held low and WE high at the rising edge of the clock, the chip enters the Auto-

Refresh mode. All banks of the SDRAM must be precharged and idle for a minimum of the Precharge time

(tRP) before the Auto-Refresh Command can be applied. An internal address counter supplies the addresses

during the refresh cycle. No control of the external address bus is required once this cycle has started.

When the refresh cycle has completed, all banks of the SDRAM will be in the precharged (idle) state. A delay

between the Auto-Refresh Command and the next Activate Command or subsequent Auto-Refresh Com-

mand must be greater than or equal to the Auto-Refresh cycle time (tRFC).

To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute

refresh interval is provided. A maximum of eight Auto-Refresh commands can be posted to any given DDR2

SDRAM, meaning that the maximum absolute interval between any Auto-Refresh command and the next

Auto-Refresh command is 9 * tREFI.

T0

T2

T1

T3

AR

CK, CK

CMD

Precharge

> = t

RP

NOP

AUTO

REFRESH

ANY

NOP

> = t

RFC

> = t

RFC

AUTO

REFRESH

NOP

CKE

"high"

相关PDF资料 |

PDF描述 |

|---|---|

| V59C1G01808QALF37E | 128M X 8 DDR DRAM, BGA68 |

| V59C1G01808QAUF37H | 128M X 8 DDR DRAM, PBGA68 |

| V59C1512804QALP19A | 64M X 8 DDR DRAM, PBGA68 |

| V59C1512804QAUF19AI | 64M X 8 DDR DRAM, PBGA68 |

| V59C1512804QAUP19AH | 64M X 8 DDR DRAM, PBGA68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

发布紧急采购,3分钟左右您将得到回复。