参数资料

| 型号: | IP-SRAM/QDRII |

| 厂商: | Altera |

| 文件页数: | 20/68页 |

| 文件大小: | 0K |

| 描述: | IP QDRII SRAM CONTROLLER |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | QDRII SRAM 控制器 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

�� �

�

�

�QDRII� SRAM� Controller� Walkthrough�

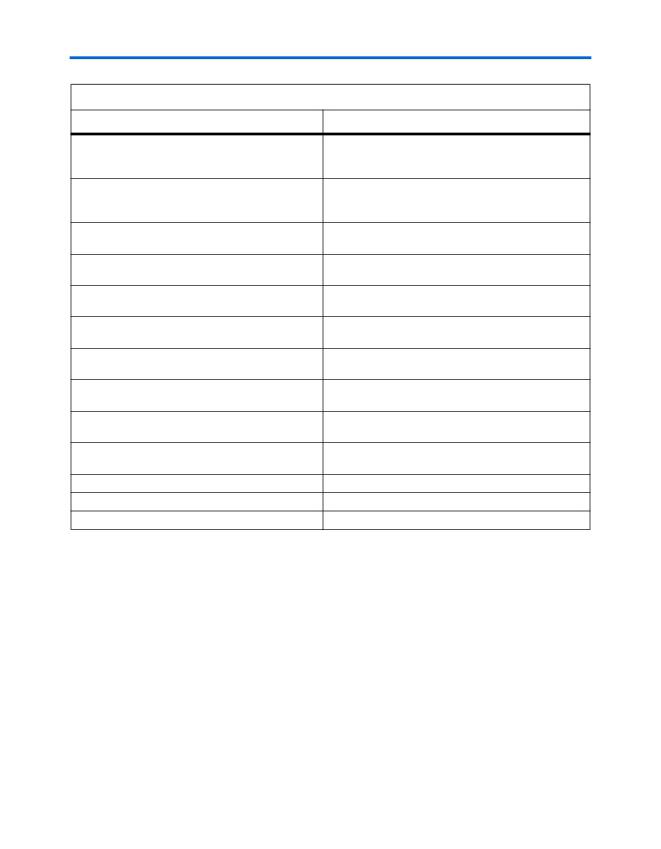

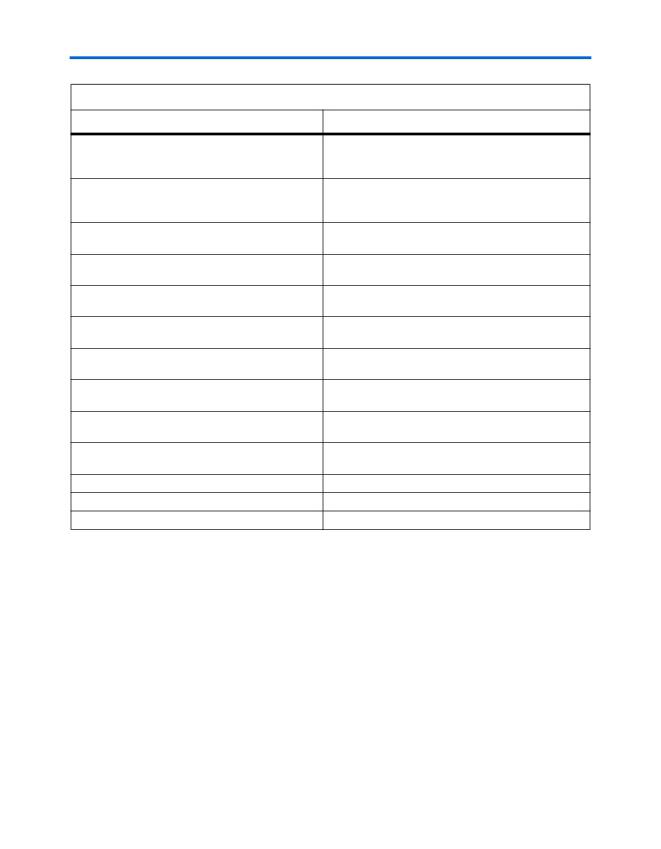

�Table� 2–1.� Generated� Files� (Part� 2� of� 2)� (1)� ,� (2)� &� (3)�

�<variation�

�Filename�

�Description�

�File� that� includes� the� w� rite� data� pipeline� and� includes� the�

�name>� _auk_� q� drii_sram_pipe_resynch_wrapper.v� address� and� command,� read� command,� w� rite� data,� and�

�hd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_pipeline_addr_cmd.vhd�

�or� .v�

�<variation�

�name>� _auk_� q� drii_sram_pipeline_rdata.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_pipeline_wdata.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_read_group.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_resynch_reg.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_train_wrapper.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_test_group.vhd� or� .v�

�<variation�

�name>� _auk_� q� drii_sram_write_group.vhd� or� .v�

�<� variation� name� >� .� q� ip�

�<top-level� name>� .vhd� or� .v� (1)�

�add_constraints_for_� <variation� name>� .tcl�

�q� drii_pll_stratixii.vhd� or� .v�

�Notes� to� Table� 2–1� :�

�w� rite� command� pipeline.�

�Address� and� command� pipeline.�

�Read� data� pipeline.�

�Write� data� pipeline.�

�The� read� registers.�

�The� resynchronization� FIFO� buffers.�

�File� that� contains� all� the� training� group� modules.�

�Training� module,� w� hich� realigns� latency.�

�The� w� rite� registers.�

�Contains� Quartus� II� project� information� for� your�

�MegaCore� function� variations.�

�Example� design� file.�

�The� add� constraints� script.�

�Stratix� II� PLL.�

�(1)�

�(2)�

�(3)�

�<� top-level� name� >� is� the� name� of� the� Quartus� II� project� top-level� entity.�

�<� variation� name� >� is� the� name� you� give� to� the� controller� you� create� with� the� Megawizard.�

�IP� Tooblench� replaces� the� string� qdrii_sram� with� qdriiplus_sram� for� QDRII+� SRAM� controllers.�

�2.�

�After� you� review� the� generation� report,� click� Exit� to� close� IP�

�Toolbench.�

�You� have� finished� the� walkthrough.� Now,� simulate� the� example� design�

�(refer� to� “Simulate� the� Example� Design”� on� page� 2–11� ),� edit� the� PLL(s)�

�(refer� to� “Edit� the� PLL”� on� page� 2–18� ),� and� compile� (refer� to� “Compile� the�

�Example� Design”� on� page� 2–19� ).�

�2–10� MegaCore� Version� 9.1�

�Altera� Corporation�

�QDRII� SRAM� Controller� MegaCore� Function� User� Guide�

�November� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP-VITERBI/SS | IP VITERBI LOW-SPEED |

| IP4220CZ6,125 | IC USB DUAL ESD PROTECT 6TSOP |

| IPA-66-1-600-10.0-A-01-T | CIRC BRKR 10A 2POLE SCREW TERM |

| IPR-CSC | IP COLOR SPACE CONVERTER RENEW |

| IPR-ED8B10B | IP 8B10B ENCODER/DECODER RENEW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPSR-AXIBFM | 功能描述:开发软件 Mentor Graphics AXI Verification RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPSR-BASE | 功能描述:开发软件 IP Base Suite MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPSR-EMBEDDED | 功能描述:开发软件 Embedded IP Suite MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPSR-VIDEO | 功能描述:开发软件 Video & Image Proc MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPSR-WMD | 功能描述:IP WIRELSS MOD/DEMOD SUITE RENEW RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

发布紧急采购,3分钟左右您将得到回复。