- 您现在的位置:买卖IC网 > PDF目录67723 > ISP1561BM,557 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 PDF资料下载

参数资料

| 型号: | ISP1561BM,557 |

| 厂商: | ST-ERICSSON |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-420-1, LQFP-128 |

| 文件页数: | 11/103页 |

| 文件大小: | 457K |

| 代理商: | ISP1561BM,557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页

ISP1561_2

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 02 — 5 March 2007

15 of 103

NXP Semiconductors

ISP1561

HS USB PCI Host Controller

8.2.1.3

Command register (address: 04h)

This is a 2-byte register that provides coarse control over the ability of a device to

generate and respond to PCI cycles. The bit allocation of the Command register is given

in Table 6. When logic 0 is written to this register, the device is logically disconnected from

the PCI bus for all accesses, except conguration accesses. All devices are required to

support this base level of functionality. Individual bits in the Command register may or may

not support this base level of functionality.

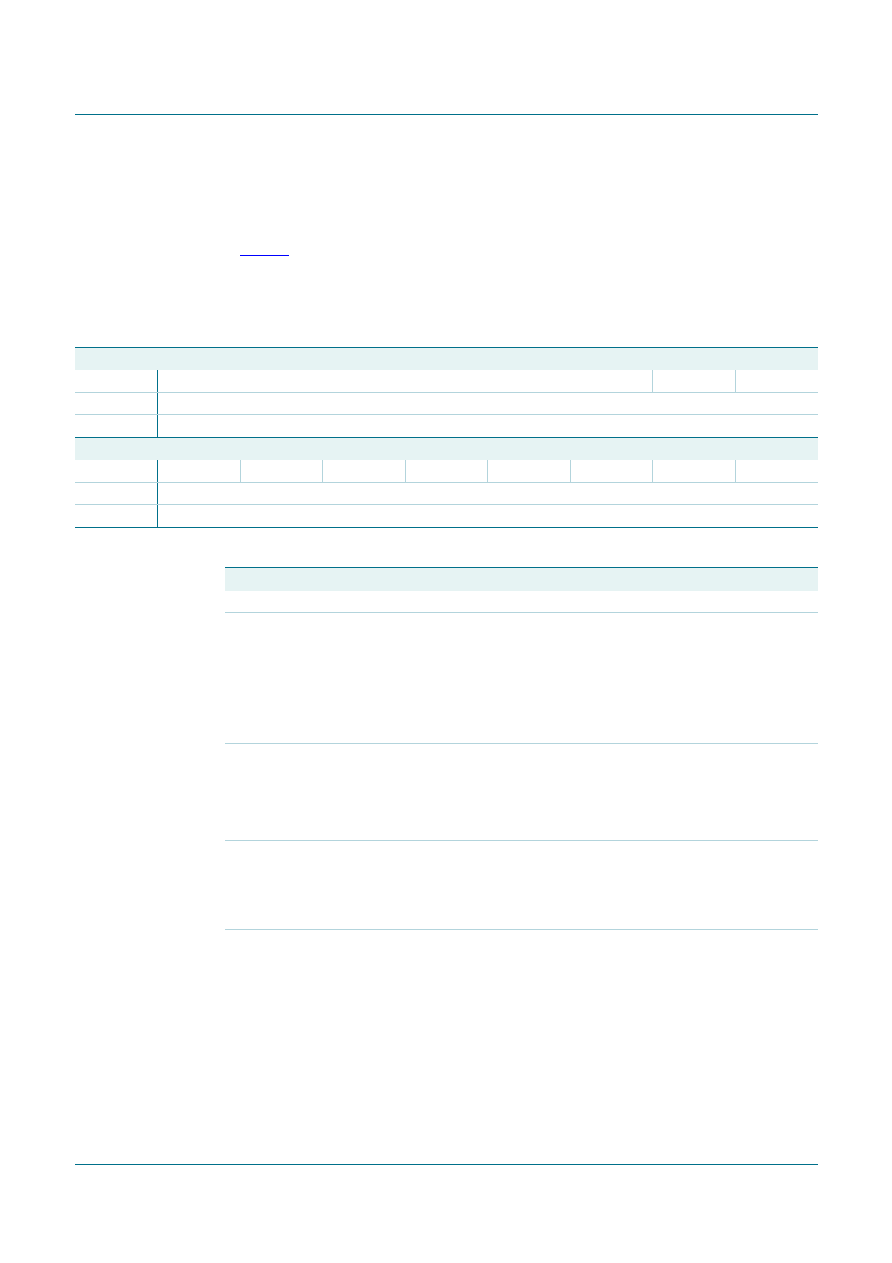

Table 6.

Command register: bit allocation

Bit

15

14

13

12

11

10

9

8

Symbol

reserved

FBBE

SERRE

Reset

00000000

Access

------

R/W

Bit

7

6

5

4

3

2

1

0

Symbol

SCTRL

PER

VGAPS

MWIE

SC

BM

MS

IOS

Reset

00000000

Access

R

R/W

R

R/W

R

R/W

Table 7.

Command register: bit description

Bit

Symbol

Description

15 to 10

-

reserved

9

FBBE

Fast Back-to-Back Enable: This bit controls whether a master can do

fast back-to-back transactions to various devices. The initialization

software must set this bit if all targets are fast back-to-back capable.

0 — Fast back-to-back transactions are only allowed to the same

agent (value after RST#).

1 — The master is allowed to generate fast back-to-back transactions

to different agents.

8

SERRE

SERR# Enable: This bit is an enable bit for the SERR# driver. All

devices that have an SERR# pin must implement this bit. Address

parity errors are reported only if this bit and the PER bit are logic 1.

0 — Disable the SERR# driver.

1 — Enable the SERR# driver.

7

SCTRL

Stepping Control: This bit controls whether a device does address

and data stepping. Devices that never do stepping must clear this bit.

Devices that always do stepping must set this bit. Devices that can do

either, must make this bit read/write and initialize it to logic 1 after

RST#.

6

PER

Parity Error Response: This bit controls the response of a device to

parity errors. When the bit is set, the device must take its normal

action when a parity error is detected. When the bit is logic 0, the

device sets its Detected Parity Error status bit (bit 15 in the Status

register) when an error is detected, but does not assert PERR# and

continues normal operation. The state of this bit after RST# is logic 0.

Devices that check parity must implement this bit. Devices are

required to generate parity, even if parity checking is disabled.

相关PDF资料 |

PDF描述 |

|---|---|

| ISP1561BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1563BM | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1563BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1564ET,551 | PCI BUS CONTROLLER, PBGA100 |

| ISP1582BS,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISP1561BMGA | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMGE | 功能描述:IC USB PCI HOST CTRLR 128-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMUM | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1562 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

| ISP1562BE | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

发布紧急采购,3分钟左右您将得到回复。