- 您现在的位置:买卖IC网 > PDF目录67723 > ISP1561BM,557 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 PDF资料下载

参数资料

| 型号: | ISP1561BM,557 |

| 厂商: | ST-ERICSSON |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-420-1, LQFP-128 |

| 文件页数: | 39/103页 |

| 文件大小: | 457K |

| 代理商: | ISP1561BM,557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页

ISP1561_2

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 02 — 5 March 2007

40 of 103

NXP Semiconductors

ISP1561

HS USB PCI Host Controller

11.1.4 HcInterruptStatus register (address: content of the base address register +

0Ch)

This is a 4-byte register that provides the status of the events that cause hardware

interrupts. The bit allocation of the register is given in Table 49. When an event occurs, the

Host Controller sets the corresponding bit in this register. When a bit becomes set, a

hardware interrupt is generated if the interrupt is enabled in the HcInterruptEnable register

(see Table 51) and the MIE (Master Interrupt Enable) bit is set. The HCD may clear

specic bits in this register by writing logic 1 to the bit positions to be cleared. The HCD

may not set any of these bits. The Host Controller does not clear the bit.

1

CLF

Control List Filled: This bit is used to indicate whether there are any TDs

on the control list. It is set by the HCD whenever it adds a TD to an ED in

the control list.

When the Host Controller begins to process the head of the control list, it

checks CLF. If CLF is logic 0, the Host Controller does not need to

process the control list. If Control-Filled (CF) is logic 1, the Host Controller

must start processing the control list and set CLF to logic 0. If the Host

Controller nds a TD on the list, then the Host Controller must set CLF to

logic 1, causing the control list processing to continue. If no TD is found

on the control list, and if the HCD does not set CLF, then CLF is still

logic 0 when the Host Controller completes processing the control list and

the control list processing stops.

0

HCR

Host Controller Reset: This bit is set by the HCD to initiate a software

reset of the Host Controller. Regardless of the functional state of the Host

Controller, it moves to the USBSUSPEND state in which most of the

operational registers are reset, except those stated otherwise; for

example, the IR (Interrupt Routing) eld of HcControl, and no host bus

accesses are allowed. This bit is cleared by the Host Controller on

completing the reset operation. The reset operation must be completed

within 10

s. This bit, when set, must not cause a reset to the root hub

and no subsequent reset signaling must be asserted to its downstream

ports.

Table 48.

HcCommandStatus register: bit description …continued

Bit

Symbol

Description

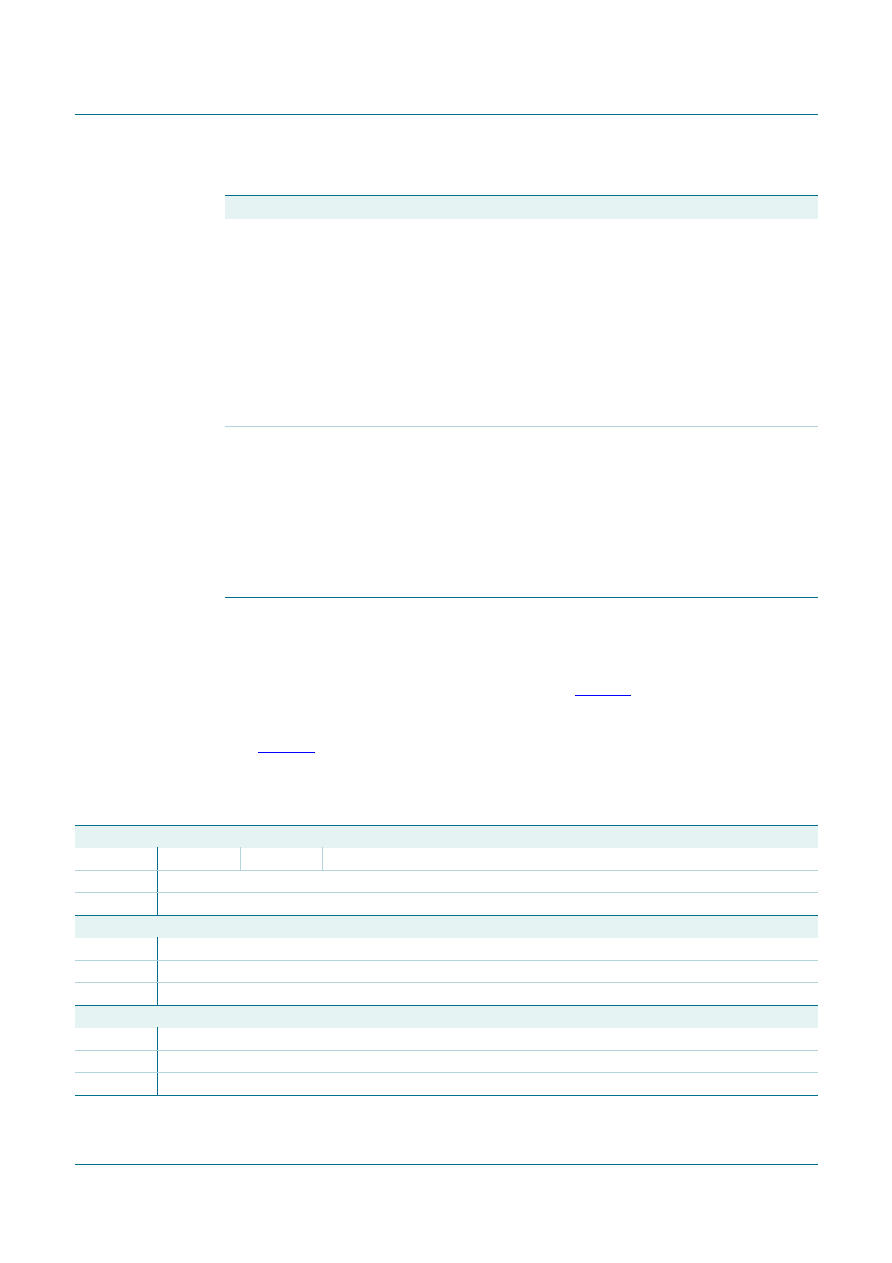

Table 49.

HcInterruptStatus register: bit allocation

Bit

31

30

29

28

27

26

25

24

Symbol

reserved

OC

reserved

Reset

00000000

Access

-

R/W

------

Bit

23

22

21

20

19

18

17

16

Symbol

reserved

Reset

00000000

Access

--------

Bit

15

14

13

12

11

10

9

8

Symbol

reserved

Reset

00000000

Access

--------

相关PDF资料 |

PDF描述 |

|---|---|

| ISP1561BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1563BM | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1563BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1564ET,551 | PCI BUS CONTROLLER, PBGA100 |

| ISP1582BS,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISP1561BMGA | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMGE | 功能描述:IC USB PCI HOST CTRLR 128-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMUM | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1562 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

| ISP1562BE | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

发布紧急采购,3分钟左右您将得到回复。