- 您现在的位置:买卖IC网 > PDF目录67723 > ISP1561BM,557 (ST-ERICSSON) UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 PDF资料下载

参数资料

| 型号: | ISP1561BM,557 |

| 厂商: | ST-ERICSSON |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-420-1, LQFP-128 |

| 文件页数: | 13/103页 |

| 文件大小: | 457K |

| 代理商: | ISP1561BM,557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页

ISP1561_2

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 02 — 5 March 2007

17 of 103

NXP Semiconductors

ISP1561

HS USB PCI Host Controller

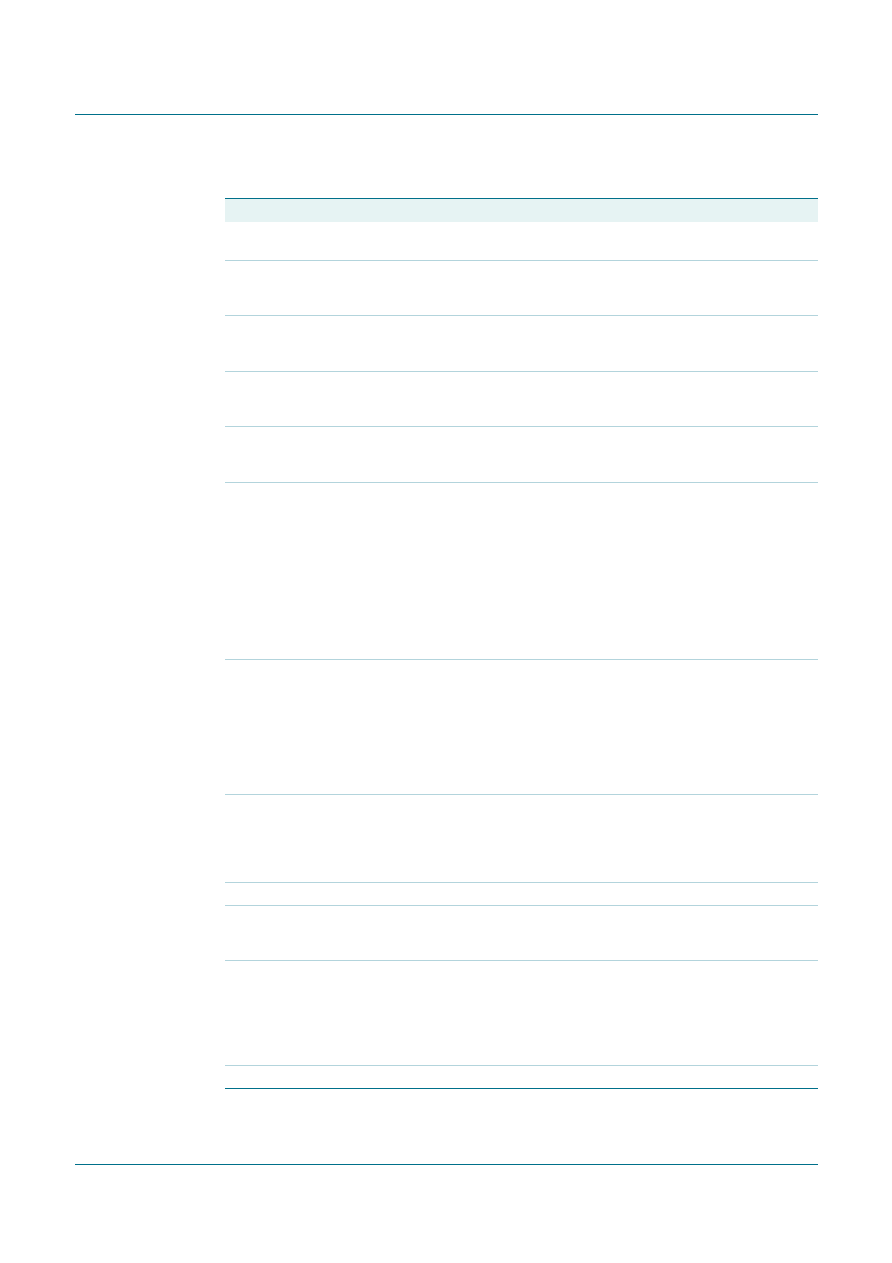

Table 9.

Status register: bit description

Bit

Symbol

Description

15

DPE

Detected Parity Error: This bit must be set by the device whenever

it detects a parity error, even if the parity error handling is disabled.

14

SSE

Signaled System Error: This bit must be set whenever the device

asserts SERR#. Devices that never assert SERR# do not need to

implement this bit.

13

RMA

Received Master Abort: This bit must be set by a master device

whenever its transaction, except for special cycle, is terminated with

master abort. All master devices must implement this bit.

12

RTA

Received Target Abort: This bit must be set by a master device

whenever its transaction is terminated with target abort. All master

devices must implement this bit.

11

STA

Signaled Target Abort: This bit must be set by a target device

whenever it terminates a transaction with target abort. Devices that

never signal target abort do not need to implement this bit.

10 to 9

DEVSELT[1:0]

DEVSEL Timing: These bits encode the timing of DEVSEL#. There

are three allowable timing for assertion of DEVSEL#:

00b — for fast

01b — for medium

10b — for slow

11b — is reserved

These bits are read-only and must indicate the slowest time that a

device asserts DEVSEL# for any bus command, except

Conguration Read and Conguration Write.

8

MDPE

Master Data Parity Error: This bit is implemented by bus masters.

It is set when the following three conditions are met:

The bus agent asserted PERR# itself, on a read; or observed

PERR# asserted, on a write.

The agent setting the bit acted as the bus master for the

operation in which error occurred.

The Parity Error Response bit (in the Command register) is set.

7

FBBC

Fast Back-to-Back Capable: This read-only bit indicates whether

the target is capable of accepting fast back-to-back transactions

when the transactions are not to the same agent. This bit can be set

to logic 1 if the device can accept these transactions; and must be

set to logic 0 otherwise.

6

-

reserved

5

66MC

66 MHz Capable: This read-only bit indicates whether this device is

capable of running at 66 MHz. A value of logic 0 indicates 33 MHz,

and a value of logic 1 indicates 66 MHz.

4CL

Capabilities List: This read-only bit indicates whether this device

implements the pointer for a new capabilities linked list at offset 34h.

A value of logic 0 indicates that no new capabilities linked list is

available. A value of logic 1 indicates that the value read at offset

34h is a pointer in conguration space to a linked list of new

capabilities.

3 to 0

-

reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ISP1561BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP128 |

| ISP1563BM | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1563BM,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQFP100 |

| ISP1564ET,551 | PCI BUS CONTROLLER, PBGA100 |

| ISP1582BS,557 | UNIVERSAL SERIAL BUS CONTROLLER, PQCC56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISP1561BMGA | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMGE | 功能描述:IC USB PCI HOST CTRLR 128-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1561BMUM | 功能描述:IC USB HOST CTRL HI-SPD 128LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| ISP1562 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

| ISP1562BE | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Hi-Speed USB PCI host controller |

发布紧急采购,3分钟左右您将得到回复。