- 您现在的位置:买卖IC网 > PDF目录180051 > M-ORT82G52BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | M-ORT82G52BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 62/94页 |

| 文件大小: | 2104K |

| 代理商: | M-ORT82G52BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

Lattice Semiconductor

ORCA ORT82G5 Data Sheet

65

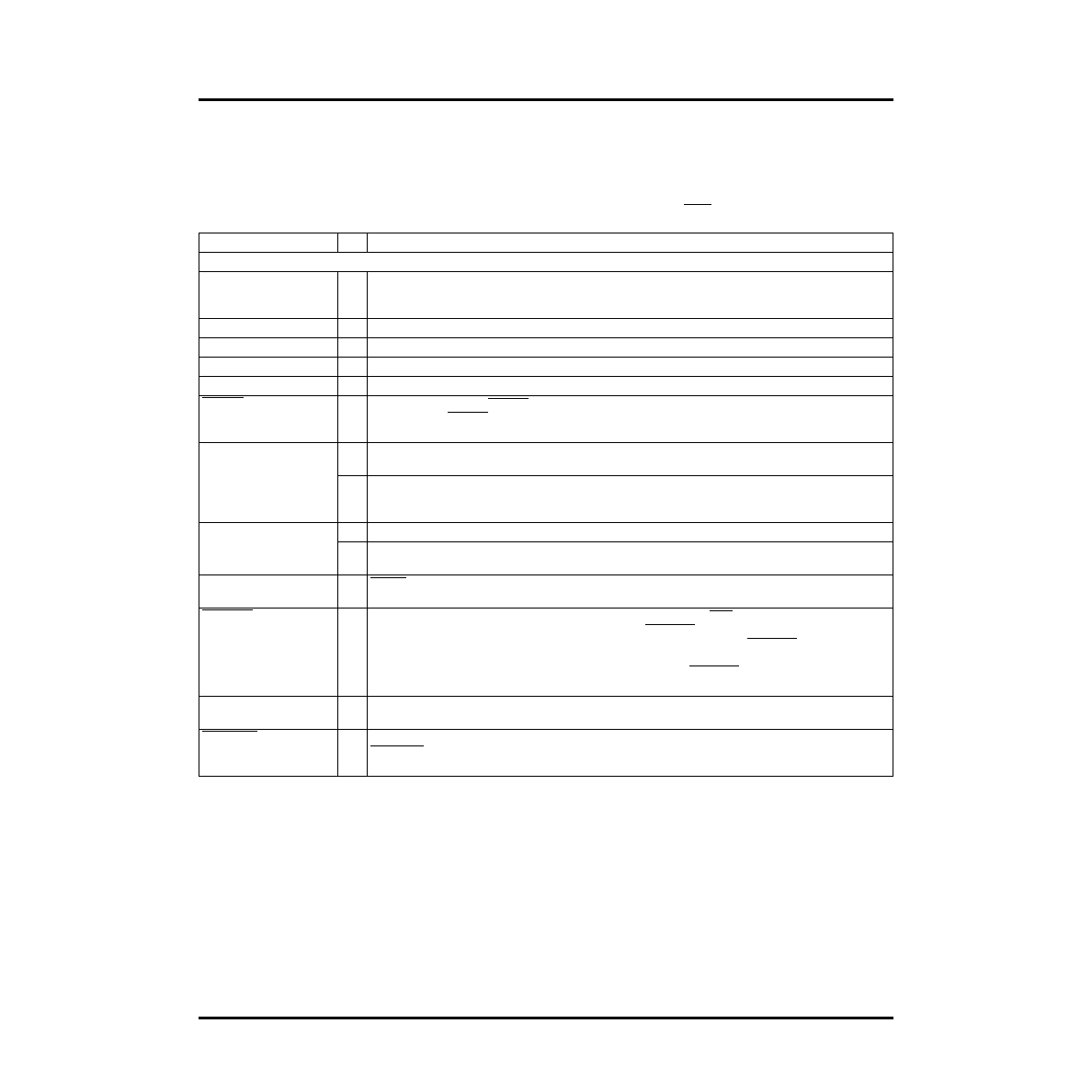

Pin Descriptions

This section describes the pins found on the Series 4 FPGAs. Any pin not described in this table is a user-program-

mable I/O. During conguration, the user-programmable I/Os are 3-stated with an internal pull-up resistor. If any pin

is not used (or not bonded to a package pin), it is also 3-stated with an internal pull-up resistor after conguration.

The pin descriptions in Table and throughout this data sheet show active-low signals with an overscore. The pack-

age pinout tables that follow, show this as a signal ending with _N. For example LDC and LDC_N are equivalent.

Symbol

I/O

Description

Dedicated Pins

VDD33

— 3.3V positive power supply. This power supply is used for 3.3 V conguration RAMs and internal

PLLs. When using PLLs, this power supply should be well isolated from all other power supplies

on the board for proper operation.

VDD

15

— 1.5 V positive power supply for internal logic.

VDDIO

— Positive power supply used by I/O banks.

VSS

— Ground.

PTEMP

I

Temperature sensing diode pin. Dedicated input.

RESET

I

During conguration, RESET forces the restart of conguration and a pull-up is enabled. After

conguration, RESET can be used as a general FPGA input or as a direct input, which causes

all PLC latches/FFs to be asynchronously set/reset.

CCLK

O

In the master and asynchronous peripheral modes, CCLK is an output which strobes congura-

tion data in.

I

In the slave or readback after conguration, CCLK is input synchronous with the data on DIN or

D[7:0]. CCLK is an output for daisy-chain operation when the lead device is in master, periph-

eral, or system bus modes.

DONE

I

As an input, a low level on DONE delays FPGA start-up after conguration.*

O

As an active-high, open-drain output, a high level on this signal indicates that conguration is

complete. DONE has an optional pull-up resistor.

PRGM

I

PRGM

is an active-low input that forces the restart of conguration and resets the boundary-

scan circuitry. This pin always has an active pull-up.

RD_CFG

I

This pin must be held high during device initialization until the INIT pin goes high. This pin

always has an active pull-up. During conguration, RD_CFG is an active-low input that activates

the TS_ALL function and 3-states all of the I/O.

After conguration, RD_CFG can be selected

(via a bit stream option) to activate the TS_ALL function as described above, or, if readback is

enabled via a bit stream option, a high-to-low transition on RD_CFG will initiate readback of the

conguration data, including PFU output states, starting with frame address 0.

RD_DATA/TDO

O

RD_DATA/TDO is a dual-function pin. If used for readback, RD_DATA provides conguration

data out. If used in boundary-scan, TDO is test data out.

CFG_IRQ/MPI_IRQ

O

During JTAG, slave, master, and asynchronous peripheral conguration assertion on this

CFG_IRQ

(active-low) indicates an error or errors for block RAM or FPSC initialization.

MPI

active-low interrupt request output, when the MPI is used.

相关PDF资料 |

PDF描述 |

|---|---|

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M01-016-1443PA | 16 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M0302CS-9N2XJSU | 1 ELEMENT, 0.0092 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| M0302CS-7N4XJSW | 1 ELEMENT, 0.0074 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

发布紧急采购,3分钟左右您将得到回复。