- 您现在的位置:买卖IC网 > PDF目录180051 > M-ORT82G52BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | M-ORT82G52BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 9/94页 |

| 文件大小: | 2104K |

| 代理商: | M-ORT82G52BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

Lattice Semiconductor

ORCA ORT82G5 Data Sheet

17

Since this effect is predictable for a given type of PCB material, it is possible to compensate for this effect in two

ways - transmitter preemphasis and receiver equalization. Each of these techniques boosts the high frequency

components of the signal but transmit preemphasis is preferred due to the ease of implementation and the better

power utilization. It also gives a better signal-to-noise ratio because receiver equalization amplies both the signal

and the noise at the receiver

Applying too much preemphasis when it is not required, for example when driving a short backplane path, will also

degrade the data eye opening at the receiver. In the ORT82G5 the degree of transmit preemphasis can be pro-

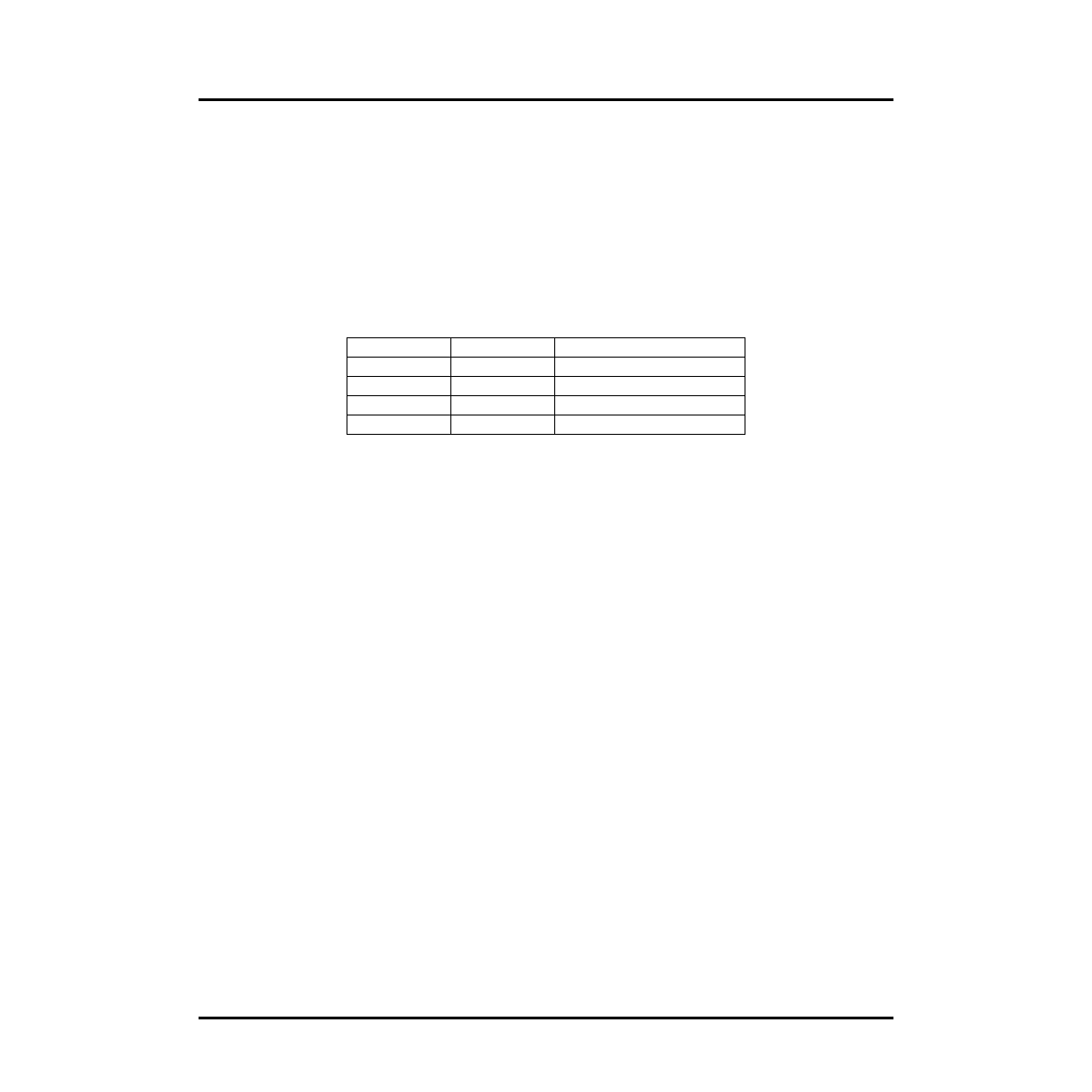

grammed with a two-bit control from the microprocessor interface as shown in Table 3. The high-pass transfer func-

tion of the preemphasis circuit is given by the following equation, where the value of a is shown in Table 3.

H(z) = (1 – az

–1)

(1)

Table 3. Preemphasis Settings

Receive Path (Backplane → FPGA) Logic

The receiver section receives high-speed serial data at the external differential CML input pins. These data are fed

to the clock recovery section which generates a recovered clock and retimes the data. Therefore the receive clocks

are asynchronous between channels. The retimed data are deserialized and presented as a 10-bit encoded or a 8-

bit unencoded parallel data on the output port. The receiver also optionally recognizes comma characters, detects

code violations and aligns the bit stream to the proper word boundary.

As shown in Figure 6, the basic blocks in the receive path include:

Receive SERDES Block

CML input buffer

Receive PLL

1:10 demultiplexer (DEMUX)

Clock and Data Recovery (CDR) section

PRBS checker

10B/8B decoder

1:4 demultiplexer and Embedded Core/FPGA interface

1:4 DEMUX

Low speed parallel Embedded Core/FPGA logic interface

Multi-channel alignment logic

PE1

PE0

Amount of Preemphasis (a)

0

0% (No Preemphasis)

0

1

12.5%

1

0

12.5%

1

25%

相关PDF资料 |

PDF描述 |

|---|---|

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M01-016-1443PA | 16 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M0302CS-9N2XJSU | 1 ELEMENT, 0.0092 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| M0302CS-7N4XJSW | 1 ELEMENT, 0.0074 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

发布紧急采购,3分钟左右您将得到回复。