- 您现在的位置:买卖IC网 > PDF目录4580 > IDT88P8341BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8341BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 19/96页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8341BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

26

IDT88P8341 SPI EXCHANGE SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

Erroneous operation

SPI-3 ingress buffers marked with an address parity error are always

immediately flushed. A SPI-3 flush event is generated.

Store process

The process parameters are stored in a descriptor table. One entry in the

table is required for each of the SPI-3 logical ports. Refer to Table 49, SPI-3

ingress LP to LID Map.

FragmentstaggedwithanSOPindicationtriggerthebuffersegmentrequest

process. The internal Packet_length variable is initialized. The copy process

is triggered.

FragmentstaggedwithanEOPindicationwilltriggerthepacketlengthcheck

process and the queue process.

Non marked (EOP or SOP) buffers are subject to the copy process.

Buffer segment request process

Anewbuffersegmentisrequestedforthelogicalportfromthebuffersegment

pool.

The request can be accepted or rejected by the buffer pool.

When accepted, the Current_Seg and current Seg_Length variables are

updated.

When rejected, the SPI-3 ingress buffer is flushed. An SPI-3 flush event is

generated and directed towards the Table 61, Non LID associated event

counters (0x00 - 0x0B). The buffer data is not copied into the SPI3-4 buffer.

Copy process

Data is retrieved from the buffer and stored in the current segment. The data

parity error status is stored in the Pack_Err variable. The Packet_Length

variables and Seg_Length variables are updated. The queue and request

processesaretriggeredwhenthenumberofbytesinthebuffersegmentequals

the SPI-3 packet fragment size programmed for that physical interface, or an

EOP is reached.

Queue process

The current segment is entered into the SPI-4 egress queue.

Packet length check

ThelengthofthepacketiscomparedtotheMIN_LENGTHandMAX_LENGTH

parametersintheingressSPI-3Portdescriptortable.Ifthepacketlengthisless

than the programmed field MIN_LENGTH a “SPI-3 too short packet event” is

generated.IfthepacketlengthisgreaterthantheprogrammedfieldMAX_LENGTH

a “SPI-3 too long packet event” is generated. The events are directed towards

the Table 61, Non LID associated event counters (0x00 - 0x0B).

SPI-3 to SPI-4 buffer management

A 128 KB SPI-3 to SPI-4 buffer segment pool is assigned to each physical

SPI-3 ingress port. A configurable part of this buffer segment pool is assigned

to buffers associated to each of the up to 64 LIDs. The buffer size for a LID can

be configured in multiples (M) of 256 bytes. Fewer LIDs allow larger buffers per

LID, conversely a large number of LIDs will require smaller buffers per LID.

Within this restriction, the buffer size of each LID can be further restricted as

needed to control latency. Modifications of the buffer size allocated to a LID are

supportedonlywhenthelogicalportassociatedtotheLIDisdisabled.Attempts

to allocate more memory than available will generate an allocation error event.

The indirect access module will discard the attempt.

Free buffer segment pool

Storage

The buffer segment pool is divided into 508 segments. The device holds a

pooloffreebuffersegments.Thebuffersegmentpoolkeepstrackofthenumber

of segments assigned to each LID and holds a list of free segments.

Buffer segment requests

A new segment for a logical Link (LID) can be requested from the buffer

segment pool for that SPI-3 ingress physical port by the SPI-3 ingress packet

fragment processor associated to that SPI-3 physical port. A request may be

accepted immediately or rejected. When the request is accepted a buffer

segment ID is returned immediately.

Buffer segment pool returned segments

Abuffersegmentcanbereturnedtothebuffersegmentpoolwhentheegress

module releases it. This allows the segment to be used once more by the SPI-

3 ingress.

SPI-4 egress queues

Normal operation

508 SPI-4 egress queue entries are provided. They are evenly allocated

tothenumberoflogicalportsasdefinedbythestaticNR_LIDconfiguration.One

entryinthequeuecorrespondstoapacketorapacketfragmenttobeforwarded

to the SPI-4 egress interface.

SPI-3 ingress Backpressure

The module directs status signals for each of the 64 LIDs associated with a

SPI-3physicalinterfacetowardstheSPI-3ingressinterface.Thestatussignals

request to transfer more data on the logical port associated to the LID. The

available status is defined by the function (if free segments [LID] > Threshold,

status=available).

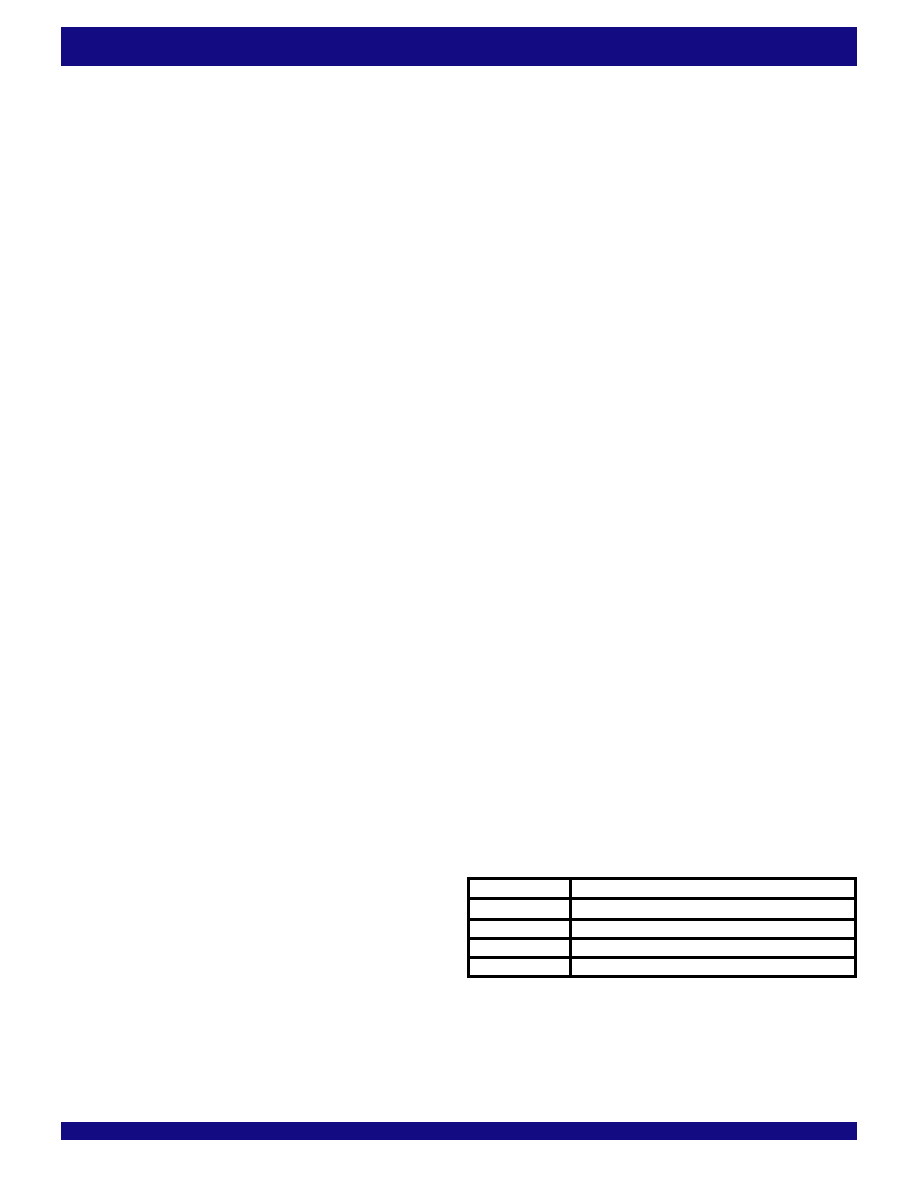

SPI-4 egress direction control

The SPI-4 egress traffic can be captured by the microprocessor, directed to

an associated SPI-3 egress port (SPI-3 port A to B, or port C to D, only), to the

SPI-4egressport,ordiscarded.Theselectionisdefinedforeachofthe64LIDs

bytheassociatedDIRECTIONfieldintheTable13,Directioncodeassignment.

DIRECTION

Path

00

SPI-4

01

AssociatedSPI-3

10

Capture to microprocessor

11

Discard

TABLE 13 - DIRECTION CODE ASSIGNMENT

相关PDF资料 |

PDF描述 |

|---|---|

| LFEC15E-4FN484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| IDT72V51446L7-5BBI | IC FLOW CTRL MULTI QUEUE 256-BGA |

| LFEC15E-4F484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| LT3022IMSE-1.8#TRPBF | IC REG LDO 1.8V 1A 16-MSOP |

| LT3022IMSE-1.5#TRPBF | IC REG LDO 1.5V 1A 16-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。