- 您现在的位置:买卖IC网 > PDF目录4580 > IDT88P8341BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8341BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 61/96页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8341BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

64

IDT88P8341 SPI EXCHANGE SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

9.3.11 Block base 0x1600 registers

The SPI-4 ingress registers are at Block_base 0x1600.

SPI-4 ingress packet length configuration

(Block_base 0x1600 + Register_offset 0x00-0x3F)

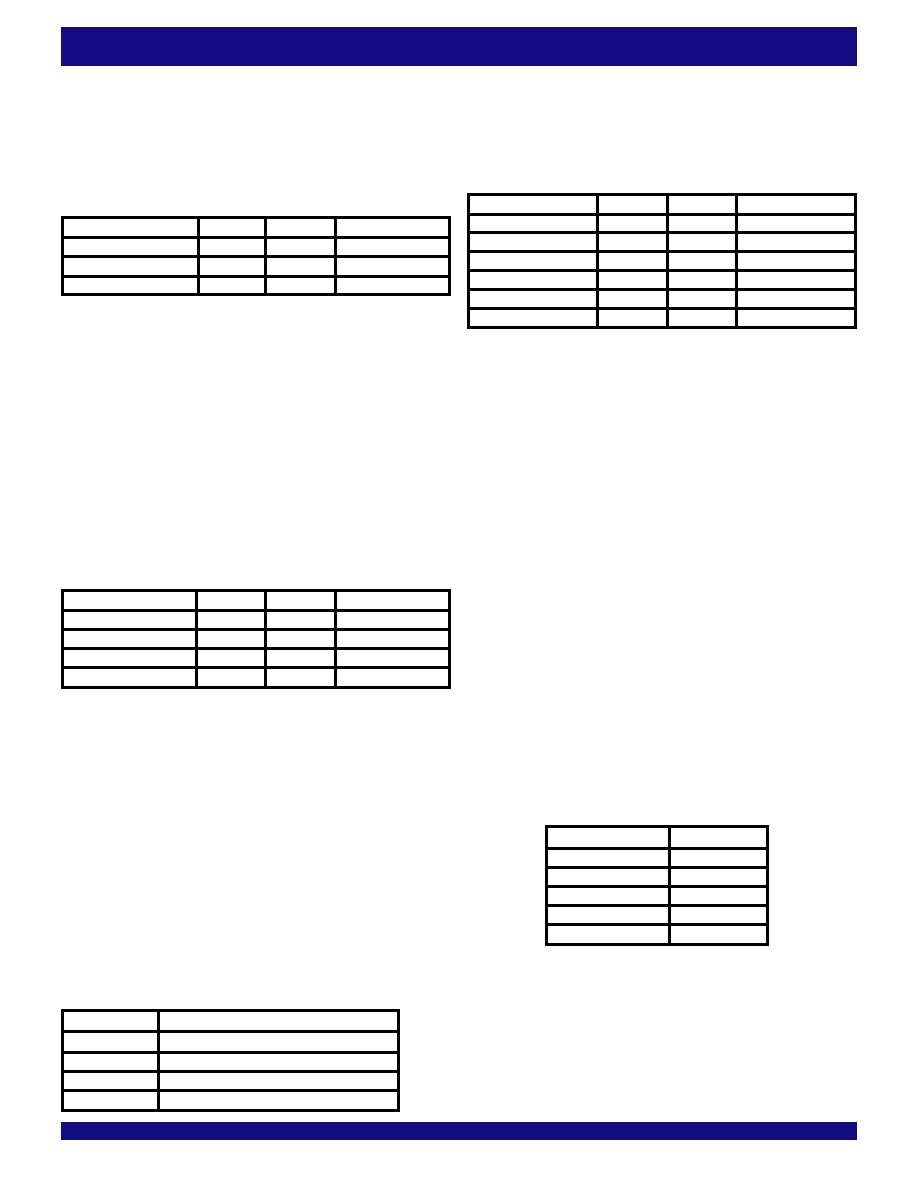

TABLE 79 - SPI-4 INGRESS PACKET LENGTH

CONFIGURATION (64 ENTRIES CONFIGURABLE)

Field

Bits

Length

Initial Value

MIN_LENGTH

7:0

8

0x40

Reserved

15:8

8

0x0

MAX_LENGTH

29:16

14

0x5EE

There is oneset of 64 registers for SPI-4 ingress packet length configuration

associatedwiththeSPI-3interface.Theregisterhasreadandwriteaccess. The

minimum and maximum packet lengths per LID are provisioned using the SPI-

4 ingress packet length configuration register. The bit fields of a SPI-4 ingress

packet length configuration register are described.

MIN_LENGTH

SPI-4 ingress minimum packet length. The minimum

packet length is programmed from 0 to 255 bytes. The resolution is one byte.

MAX_LENGTH SPI-4 ingress maximum packet length. The maximum

packetlengthisprogrammedfrom0to16,383bytes.Theresolutionisonebyte.

9.3.12 Block base 0x1700 registers

SPI-3 egress port descriptor table (Block_base

0x1700 + Register_offset 0x00-0x3F)

There are 64 SPI-3 egress port descriptor tables for the SPI-3 egress port.

The SPI-3 egress port descriptor table has read and write access. The SPI-

3 egress per LID packet fragment length and direction are provisioned using

the SPI-3 egress port descriptor tables. The bit fields of the SPI-3 egress port

descriptor table are described.

MAX_BURST

SPI-3 packet fragment length for a SPI-3 egress LP. One

morethanMAX_BURSTfieldmultipliedbysixteenisthepacketfragmentlength

fortheLP.Forexample, programmingthenumber3intotheMAX_BURSTfield

results in a packet fragment length of (3+1) x 16 = 64 bytes. The MAX_BURST

field is used to prioritize traffic.

DIRECTION

TheSPI-3egresstrafficisdirectedtoaSPI-3egressport.

The Path selection is defined for each of the 64 LIDs by the associated

DIRECTION field as shown in the following table.

TABLE 80 - SPI-3 EGRESS PORT DESCRIPTOR

TABLE (64 ENTRIES)

Field

Bits

Length

Initial Value

MAX_BURST

3:0

4

0x0F

Reserved

7:4

4

0x0

DIRECTION

8:9

2

0b11

Reserved

31:10

22

0x00

9.3.13 Block base 0x1800 registers

SPI-4 ingress port descriptor table (Block_base

0x1800 + Register_offset 0x00-0x3F)

There is one set of 64 registers for SPI-4 ingress port descriptors for the SPI-

3 interface. The SPI-4 ingress port descriptor tables are 32 bits wide and have

read and write access. Each of the SPI-4 ingress port descriptor tables is used

tocontroltheamountofbufferingandthebackpressurethresholdoftheavailable

buffer segment pool for the SPI-4 ingress.

EachSPI-4ingressbuffersegmentpoolis128Kbytes,dividedinto508buffer

segments of 256 bytes per segment. The 508 buffer segments can be shared

amongtheLIDsinitiallyprogrammedbythenumericalfieldNR_LID.Oftheshare

of the buffer memory, a SPI-4 LID can be allocated the maximum number of

segments permitted, or can be programmed to fewer segments by decreasing

the M field. Decreasing M increases the chance of backpressure and possibly

buffer overflow, but can result in lower latency.

The FREE_SEGMENT_S (starving threshold) and FREE_SEGMENT_H

(hungry threshold) fields are used, along with the M field, to set the two

backpressuresettingsperLIDontheSPI-4ingress.TheFREE_SEGMENT_S

field must always be greater than the FREE_SEGMENT_H field.

M

Thenumberof256-bytebufferpoolsegmentsallocatedtoaLID.The

range of M is 0x000 to 0x1FC (508 base 10), but can not exceed the number

dictated by NR_LID [Block_base 0x1900 + Register_offset 0x00].

FREE_SEGMENT_S

This field is used to define the SPI-4 ingress per-LID starving backpressure

threshold based on the number of free buffer pool segments (M) available, as

follows:

THRESHOLD_S = N * FREE_SEGEMENT_S, where the value of N is

defined as:

DIRECTION

Path

00

SPI-3 physical

01

Reserved

10

Capture

11

Discard

TABLE 81 - SPI-3 EGRESS DIRECTION CODE

ASSIGNMENT

TABLE 82 - SPI-4 INGRESS PORT DESCRIPTOR

TABLES (64 ENTRIES)

Field

Bits

Length

Initial Value

M

8:0

9

0x000

Reserved

15:9

7

0x00

FREE_SEGMENT_S

20:16

5

0x00

Reserved

23:21

3

0x0

FREE_SEGMENT_H

28:24

5

0x00

Reserved

31:29

3

0x0

M[8:0]

N

0x1FF to 0x100

16

0x0FF to 0x080

8

0x07F to 0x040

4

0x03F to 0x020

2

0x01F to 0x000

1

FREE_SEGMENT_H

This field is used to define the SPI-4 ingress per-LID hungry backpressure

threshold based on the number of free buffer pool segments (M) available, as

follows:

THRESHOLD_H = N * FREE_SEGEMENT_H, where the value of N is as

defined for FREE_SEGEMENT_S.

相关PDF资料 |

PDF描述 |

|---|---|

| LFEC15E-4FN484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| IDT72V51446L7-5BBI | IC FLOW CTRL MULTI QUEUE 256-BGA |

| LFEC15E-4F484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| LT3022IMSE-1.8#TRPBF | IC REG LDO 1.8V 1A 16-MSOP |

| LT3022IMSE-1.5#TRPBF | IC REG LDO 1.5V 1A 16-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。