- 您现在的位置:买卖IC网 > PDF目录4580 > IDT88P8341BHGI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF资料下载

参数资料

| 型号: | IDT88P8341BHGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 58/96页 |

| 文件大小: | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 标准包装: | 24 |

| 系列: | * |

| 其它名称: | 88P8341BHGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

61

IDT88P8341 SPI EXCHANGE SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

Non critical LID associated capture table

(Block_base 0x0C00 + Register_offset 0x10-0x15)

The Non critical LID associated capture table is at Block_Base 0x0C00 +

Register_Offset 0x10-0x15. The Non critical LID associated capture table is

used to determine the EVENT_TYPE of SPI-3 and SPI-4 per-LID or per-LP

interrupts.TheEVENT_TYPEcodingisusedtoindicatewhicheventorevents

arepertinenttotheinterruptintheTable64-LIDassociatedinterruptindication

register(0x0E). The Non critical LID associated capture table is used to

determinetheEVENT,andmultiplebitscanbeactiveatthesametime.TheNon

critical LID associated capture table is read-only.

SPI-3 to SPI-4 critical LID interrupt indication

registers (Block_base 0x0C00 + Register_offset

0x16-0x17)

TheSPI-3toSPI-4criticalLIDinterruptindicationregistersareatBlock_Base

0x0C00 + Register_offset 0x10-0x15.

CriticaleventsarecapturedperLIDintheSPI-3toSPI-4criticalLIDinterrupt

indication registers. An interrupt is generated when enabled by the enable flag

intheSPI-3toSPI-4criticalLIDinterruptenableregisters.ASPI-3toSPI-4critical

LIDinterruptindicationregisterhasreadandwriteaccess.Aninterruptindication

isclearedbywritingalogicalonetotheappropriatebitofaSPI-3toSPI-4critical

LID interrupt indication register. Only one kind of critical event is defined-buffer

overflow. Each bit of the LID field set to logical one indicates the presence of a

buffer overflow event. A summary indication of as to which of the two sources,

SPI-3toSPI-4orSPI-4toSPI-3,isresponsibleforthecriticalinterruptisindicated

in the Table 71 Critical events source indication register (0x1E).

SPI-3 to SPI-4 critical LID interrupt enable regis-

ters (Block_base 0x0C00 + Register_offset 0x18-

0x19)

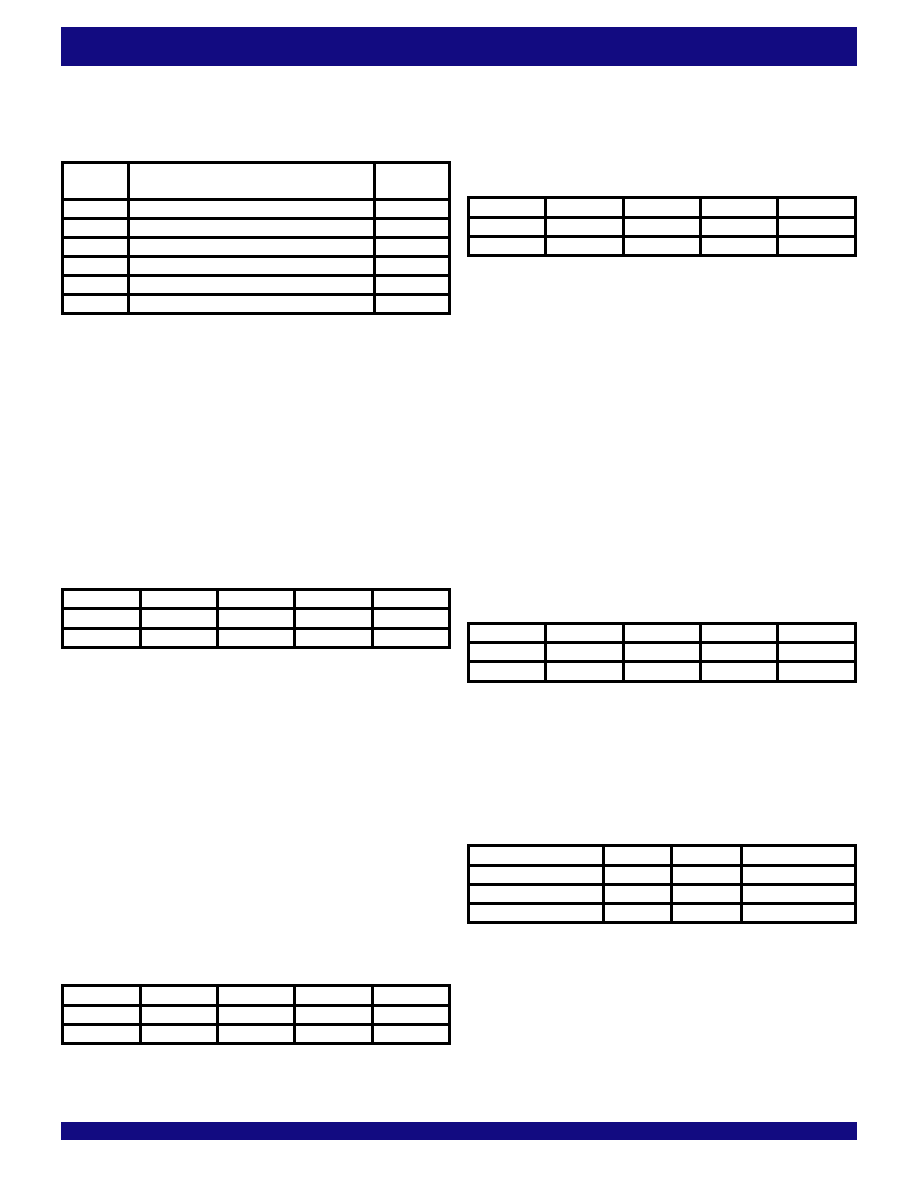

TABLE 66 - NON CRITICAL LID ASSOCIATED

CAPTURE TABLE (REGISTER_OFFSET 0x10-0x15)

Register

EVENT_TYPE

Associated

field

0x00

Inactive ingress SPI-3 logical port event

LP (8 bits)

0x01

SPI-3 ingress data parity error

LID (6 bits)

0x02

SPI-4 illegal SOP sequence event

LID (6 bits)

0x03

SPI-4 illegal EOP sequence event

LID (6 bits)

0x04

SPI-3 illegal SOP sequence event

LID (6 bits)

0x05

SPI-3 illegal EOP sequence event

LID (6 bits)

TABLE 67 - SPI-3 TO SPI-4 CRITICAL LID INTER-

RUPTINDICATIONREGISTERS

(REGISTER_OFFSET 0x16-0x17)

Register

Field

Bits

Length

Initial Value

0x16

LID[31:0]

31:0

32

0x00

0x17

LID[63:32]

31:0

32

0x00

TABLE68-SPI-3TOSPI-4CRITICALLIDINTERRUPT

ENABLE REGISTERS (REGISTER_OFFSET 0x18-

0x19)

Register

Field

Bits

Length

Initial Value

0x18

LID[31:0]

31:0

32

0x00

0x19

LID[63:32]

31:0

32

0x00

TheSPI-3toSPI-4criticalLIDinterruptenableregistershavereadandwrite

access. A SPI-3 to SPI-4 critical LID interrupt enable register bits enable the

corresponding bits in a SPI-3 to SPI-4 critical LID interrupt indication register.

SPI-4 to SPI-3 critical LID interrupt indication

registers (Block_base 0x0C00 + Register_offset

0x1A-0x1B)

TABLE69-SPI-4TOSPI-3CRITICALLIDINTERRUPT

INDICATIONREGISTERS(REGISTER_OFFSET

0x1A-0x1B)

Register

Field

Bits

Length

Initial Value

0x1A

LID[31:0]

31:0

32

0x00

0x1B

LID[63:32]

31:0

32

0x00

TheSPI-4toSPI-3criticalLIDinterruptindicationregistersareatBlock_Base

0x0C00 + Register_offset 0x1A-0x1B.

Critical events are captured per LID in a SPI-4 to SPI-3 critical LID interrupt

indication register. An interrupt is generated when enabled by the enable flag

in the SPI-4 to SPI-3 critical LID interrupt enableregister. The SPI-4 to SPI-3

criticalLIDinterruptindicationregistershavereadandwriteaccess.Aninterrupt

indication is cleared by writing a logical one to the appropriate bit of a SPI-4 to

SPI-3 critical LID interrupt indication register. Only one kind of critical event is

defined-buffer overflow. Each bit of a LID field set to logical one indicates the

presence of a buffer overflow event. A summary indication of as to which of the

two sources, SPI-3 to SPI-4 or SPI-4 to SPI-3, is responsible for the critical

interrupt is indicated in the Table 71 Critical events source indication register

(0x1E).

SPI-4 to SPI-3 critical LID interrupt enable regis-

ters (Block_base 0x0C00 + Register_offset 0x1C-

0x1D)

TABLE 70 - SPI-4 TO SPI-3 CRITICAL LID INTER-

RUPTENABLEREGISTERS(REGISTER_OFFSET

0x1C-0x1D)

Register

Field

Bits

Length

Initial Value

0x1C

LID[31:0]

31:0

32

0x00

0x1D

LID[63:32]

31:0

32

0x00

TheSPI-4toSPI-3criticalLIDinterruptenableregistershavereadandwrite

access. The SPI-4 to SPI-3 critical LID interrupt enable register bits enable the

correspondingbitsintheSPI-4toSPI-3criticalLIDinterruptindicationregisters.

Critical events source indication register

(Block_base 0x0C00 + Register_offset 0x1E)

TABLE 71 - CRITICAL EVENTS SOURCE INDICA-

TION REGISTER (REGISTER_OFFSET 0x1E)

Field

Bits

Length

Initial Value

SPI34_OVR

0

1

0b0

SPI43_OVR

1

0b0

Reserved

31:2

30

0x0

The bits in the Critical events source indication register are read only. Bit

SPI34_OVR reflects the logical OR result of all bits in the SPI-3 to SPI-4 critical

LIDassociatedinterruptindicationregisters.BitSPI43_OVRreflectsthelogical

ORresultofallbitsintheSPI-4toSPI-3criticalLIDinterruptindicationregisters.

相关PDF资料 |

PDF描述 |

|---|---|

| LFEC15E-4FN484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| IDT72V51446L7-5BBI | IC FLOW CTRL MULTI QUEUE 256-BGA |

| LFEC15E-4F484C | IC FPGA 10.2KLUTS 288I/O 484-BGA |

| LT3022IMSE-1.8#TRPBF | IC REG LDO 1.8V 1A 16-MSOP |

| LT3022IMSE-1.5#TRPBF | IC REG LDO 1.5V 1A 16-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT88P8344 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| IDT88P8344BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。