- 您现在的位置:买卖IC网 > PDF目录11210 > ADUC7061BCPZ32-RL (Analog Devices Inc)IC MCU 16/32BIT 32KB 32LFCSP PDF资料下载

参数资料

| 型号: | ADUC7061BCPZ32-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/108页 |

| 文件大小: | 0K |

| 描述: | IC MCU 16/32BIT 32KB 32LFCSP |

| 产品变化通告: | ADuC7060/1 Idd Specification Change 01/Feb/2010 |

| 设计资源: | USB Based Temperature Monitor Using ADuC7061 and an External RTD (CN0075) 4 mA-to-20 mA Loop-Powered Temperature Monitor Using ADuC7060/1 (CN0145) |

| 标准包装: | 5,000 |

| 系列: | MicroConverter® ADuC7xxx |

| 核心处理器: | ARM7 |

| 芯体尺寸: | 16/32-位 |

| 速度: | 10MHz |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | POR,PWM,温度传感器,WDT |

| 输入/输出数: | 8 |

| 程序存储器容量: | 32KB(16K x 16) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 1K x 32 |

| 电压 - 电源 (Vcc/Vdd): | 2.375 V ~ 2.625 V |

| 数据转换器: | A/D 5x24b,8x24b,D/A 1x14b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

Data Sheet

ADuC7060/ADuC7061

Rev. D | Page 23 of 108

By default, after a reset, the Flash/EE memory is logically

mapped to Address 0x00000000. It is possible to logically remap

the SRAM to Address 0x00000000 by setting Bit 0 of the remap

MMR located at 0xFFFF0220. To revert Flash/EE to 0x00000000,

Bit 0 of remap is cleared.

It is sometimes desirable to remap RAM to 0x00000000 to optimize

the interrupt latency of the ADuC706x because code can run in

full 32-bit ARM mode and at maximum core speed. Note that,

when an exception occurs, the core defaults to ARM mode.

Remap Operation

When a reset occurs on the ADuC706x, execution starts automati-

cally in the factory programmed internal configuration code.

This so-called kernel is hidden and cannot be accessed by user

code. If the ADuC706x is in normal mode, it executes the power-

on configuration routine of the kernel and then jumps to the

reset vector, Address 0x00000000, to execute the user’s reset

exception routine. Because the Flash/EE is mirrored at the

bottom of the memory array at reset, the reset routine must

always be written in Flash/EE.

The remap command must be executed from the absolute Flash/EE

address and not from the mirrored, remapped segment of memory,

because this may be replaced by SRAM. If a remap operation is

executed while operating code from the mirrored location, pre-

fetch/data aborts can occur, or the user can observe abnormal

program operation. Any kind of reset logically remaps the Flash/EE

memory to the bottom of the memory array.

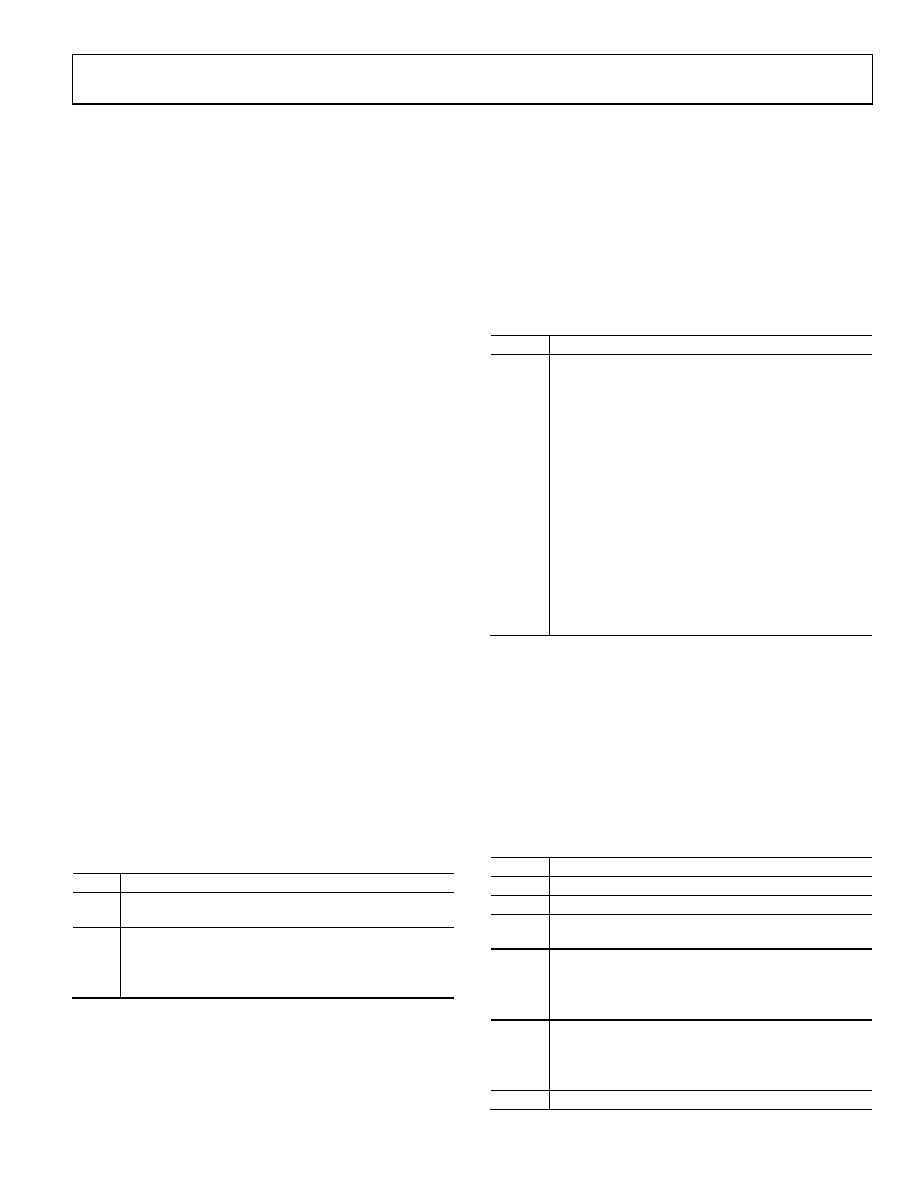

Remap Register

Name:

Remap

Address:

0xFFFF0220

Default value: 0x0000

Access:

Read and write

Function:

This 8-bit register allows user code to remap

either RAM or Flash/EE space into the bottom

of the ARM memory space starting at

Address 0x00000000.

Table 12. Remap MMR Bit Designations

Bit

Description

7:1

Reserved. These bits are reserved and should be written

as 0 by user code.

0

Remap bit.

Set by user to remap the SRAM to 0x00000000.

Cleared automatically after reset to remap the Flash/EE

memory to 0x00000000.

FLASH/EE CONTROL INTERFACE

Serial and JTAG programming use the Flash/EE control

interface, which includes the eight MMRs outlined in this

section. Note that the flash page size is 512 bytes.

FEESTA Register

FEESTA is a read-only register that reflects the status of the

flash control interface as described in Table 13.

Name:

FEESTA

Address:

0xFFFF0E00

Default value:

0x0020

Access:

Read

Table 13. FEESTA MMR Bit Designations

Bit

Description

15:6

Reserved.

5

Reserved.

4

Reserved.

3

Flash interrupt status bit. Set automatically when an

interrupt occurs, that is, when a command is complete

and the Flash/EE interrupt enable bit in the FEEMOD

register is set. Cleared when reading the FEESTA

register.

2

Flash/EE controller busy. Set automatically when the

controller is busy. Cleared automatically when the

controller is not busy.

1

Command fail. Set automatically when a command

completes unsuccessfully. Cleared automatically when

reading the FEESTA register.

0

Command pass. Set by the MicroConverter when a

command completes successfully. Cleared

automatically when reading the FEESTA register.

FEEMOD Register

FEEMOD sets the operating mode of the flash control interface.

Table 14 lists FEEMOD MMR bit designations.

Name:

FEEMOD

Address:

0xFFFF0E04

Default value:

0x0000

Access:

Read and write

Table 14. FEEMOD MMR Bit Designations

Bit

Description

15:9

Reserved.

8

Reserved. Always set this bit to 1.

7:5

Reserved. Always set these bits to 0 except when

writing keys.

4

Flash/EE interrupt enable.

Set by user to enable the Flash/EE interrupt. The

interrupt occurs when a command is complete.

Cleared by user to disable the Flash/EE interrupt.

3

Erase/write command protection.

Set by user to enable the erase and write commands.

Cleared to protect the Flash/EE against the erase/write

command.

2:0

Reserved. Always set these bits to 0.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B2L-IW-F4 | CONVERTER MOD DC/DC 28V 100W |

| ATMEGA8535L-8JU | MCU AVR 8K ISP FLASH MEM 44-PLCC |

| VI-B2L-IW-F3 | CONVERTER MOD DC/DC 28V 100W |

| ATMEGA8535L-8PU | IC AVR MCU 8K 8MHZ 3V 40DIP |

| VI-B2L-IW-F2 | CONVERTER MOD DC/DC 28V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADUC70SMARTLINKRL7 | 制造商:Analog Devices 功能描述: |

| ADUC70TEL | 制造商:Analog Devices 功能描述:FLASH ARM +5-CH 12BIT ADC - Trays |

| ADUC70TEL-RL7 | 制造商:Analog Devices 功能描述: |

| ADUC7120BBCZ | 制造商:Analog Devices 功能描述:- Rail/Tube |

| ADUC7120BBCZ-RL | 制造商:Analog Devices 功能描述:- Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。