参数资料

| 型号: | CORE1553BRT-AR |

| 厂商: | Microsemi SoC |

| 文件页数: | 15/74页 |

| 文件大小: | 0K |

| 描述: | IP MODULE CORE1553 REMOTE TERM |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

�� �

�

�

�Core1553BRT� v4.0� Handbook�

�I/O� Signal� Descriptions�

�Table� 3-2� lists� the� signals� for� the� 1553B� bus� interface.� Table� 3-3� on� page� 15� lists� the� control� and� status�

�signals.�

�Double� flip-flop� metastability� synchronizers� are� implemented� on� the� following� inputs:� RTADDR[4:0],�

�RTADDRP,� BUSAINP,� BUSAINN,� BUSBINP,� and� BUSBINN.�

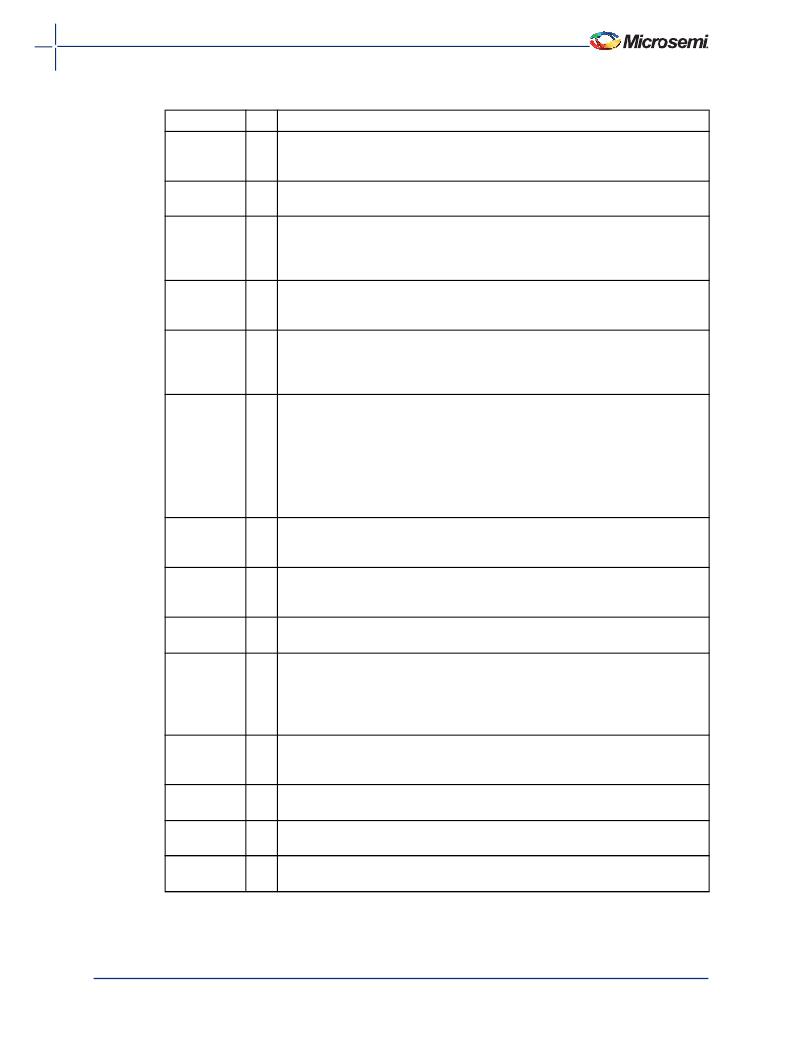

�Table� 3-2� ?� 1553B� Bus� Interface�

�Port� Name�

�RTADDR[4:0]�

�RTADDRP�

�Type�

�In�

�In�

�Description�

�Sets� the� RT� address;� RT� address� can� be� set� to� ‘11111’� for� normal� operation�

�only� when� BCASTEN� is� set� to� 0.�

�RT� address� parity� input.� This� input� should� be� set� HIGH� or� LOW� to� achieve�

�odd� parity� on� the� RTADDR� and� RTADDRP� inputs.� If� RTADDR� is� '00000',� the�

�RTADDRP� input� should� be� 1.�

�RTADERR�

�BUSAINEN�

�Out� Indicates� that� the� RTADDR� and� RTADDRP� inputs� have� incorrect� parity,� or�

�broadcast� is� enabled,� and� the� RT� address� is� set� to� 31.� When� active� (HIGH),� the� RT�

�is� disabled� and� will� ignore� all� 1553B� traffic.�

�Out� Active� high� output� that� enables� for� the� A� receiver�

�BUSAINP�

�BUSAINN�

�In�

�In�

�Positive� data� input� from� the� A� receiver�

�Negative� data� input� from� the� A� receiver�

�BUSBINEN�

�Out� Active� high� output� that� enables� for� the� B� receiver�

�BUSBINP�

�BUSBINN�

�In�

�In�

�Positive� data� input� from� the� bus� to� the� B� receiver�

�Negative� data� input� from� the� bus� to� the� B� receiver�

�BUSAOUTIN�

�BUSAOUTP�

�BUSAOUTN�

�BUSBOUTIN�

�BUSBOUTP�

�BUSBOUTN�

�Out� Active� high� transmitter� inhibit� for� the� A� transmitter�

�Out� Positive� data� output� to� the� bus� A� transmitter� (held� HIGH� when� no� transmission)�

�Out� Negative� data� output� to� the� bus� A� transmitter� (held� HIGH� when� no� transmission)�

�Out� Active� high� transmitter� inhibits� the� B� transmitter�

�Out� Positive� data� output� to� the� bus� B� transmitter� (held� HIGH� when� no� transmission)�

�Out� Negative� data� output� to� the� bus� B� transmitter� (held� HIGH� when� no� transmission)�

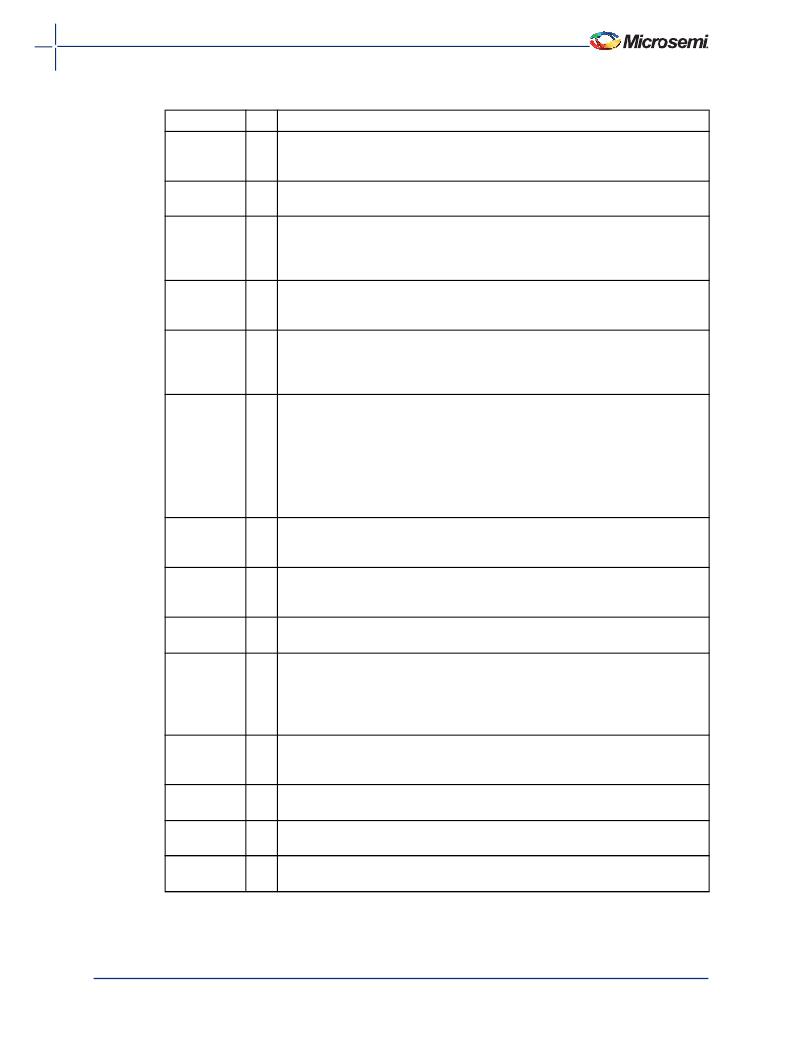

�Table� 3-3� ?� Control� and� Status� Signals�

�Port� Name�

�CLK�

�RSTn�

�SREQUEST�

�RTBUSY�

�SSFLAG�

�TFLAG�

�VWORD[15:0]�

�Type�

�In�

�In�

�In�

�In�

�In�

�In�

�In�

�Description�

�Master� clock� input� (12,� 16,� 20,� or� 24� MHz)�

�Reset� input� asynchronous� (active� low)�

�Directly� controls� the� Service� Request� bit� in� the� 1553B� status� word�

�Directly� controls� the� Busy� bit� in� the� 1553B� status� word�

�Directly� controls� the� Subsystem� Flag� bit� in� the� 1553B� status� word�

�Controls� the� Terminal� Flag� bit� in� the� 1553B� status� word.� This� can� be� masked� by� the�

�"inhibit� terminal� flag� bit"� mode� code.�

�Provides� the� 16-bit� vector� value� for� the� "transmit� vector� word"� mode� command�

�BUSY�

�Out� Indicates� that� the� 1553BRT� is� either� receiving� or� transmitting� data� or� handling� a�

�mode� command�

�Note:� All� control� inputs� except� RSTn� are� synchronous� and� sampled� on� the� rising� edge� of� the� clock.� All�

�status� outputs� are� synchronous� to� the� rising� edge� of� the� clock.�

�Revision� 3�

�15�

�相关PDF资料 |

PDF描述 |

|---|---|

| CORE8051-AR | IP MODULE CORE8051 |

| COREFFT-RM | IP MODULE COREFFT |

| COREFIR-RM | IP MODULE COREFIR |

| COREPCIF-RM | IP MODULE COREPCIF |

| COREU1LL-AR | IP MODULE COREU1LL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE1553BRT-EBR-AN | 功能描述:IP MOD CORE1553 EBR ENH BIT RATE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRT-EBR-AR | 功能描述:IP MOD CORE1553 EBR ENH BIT RATE RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRT-OM | 功能描述:IP MODULE CORE1553 REMOTE TERM RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BRT-OMFL | 功能描述:IP MODULE CORE1553 BUS/REMOTE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1 |

| CORE1553BRT-RM | 功能描述:IP MODULE CORE1553 REMOTE TERM RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

发布紧急采购,3分钟左右您将得到回复。